# AIRCRAFT DIGITAL ELECTRONIC AND COMPUTER SYSTEMS

MIKE TOOLEY

SECOND EDITION

# Aircraft Digital Electronic and Computer Systems

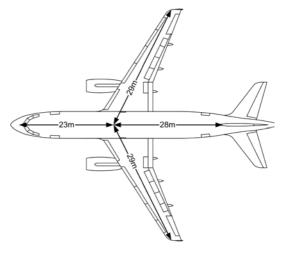

A next-generation Boeing 737 aircraft with seating for up to 190 passengers and an operational range of up to 3,000 nautical miles (5,500 km). Like all of today's aircraft, the Boeing 737-800, makes extensive use of digital electronic and computer systems

# Aircraft Digital Electronic and Computer Systems

Mike Tooley

Second edition published 2013

by Routledge

2 Park Square, Milton Park, Abingdon, Oxon OX14 4RN

Simultaneously published in the USA and Canada by Routledge

711 Third Avenue, New York, NY 10017

Routledge is an imprint of the Taylor & Francis Group, an informa business

© 2013 Mike Tooley

The right of Mike Tooley to be identified as author of this work has been asserted by him in accordance with sections 77 and 78 of the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this book may be reprinted or reproduced or utilised in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage or retrieval system, without permission in writing from the publishers.

Trademark notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

First edition published by Butterworth-Heinemann 2007

British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

Library of Congress Cataloging in Publication Data

Tooley, Michael H.

Aircraft digital electronic and computer systems / Mike Tooley. — Second edition.

pages cm

Includes index.

- 1. Airplanes—Electronic equipment—Examinations—Study guides.

- 2. Digital avionics—Examinations—Study guides. I. Title.

TL693.T665 2013

629.135'5-dc23

2012045706

ISBN: 978-0-415-82860-4 (pbk) ISBN: 978-0-203-50773-5 (ebk)

Typeset in Perpetua

by Keystroke, Station Road, Codsall, Wolverhampton

# **Contents**

| Preface    |                                                    | ix   |

|------------|----------------------------------------------------|------|

| Acknowledg | gements                                            | xiii |

| Chapter 1  | Introduction                                       | 1    |

| •          | Flight instruments                                 | 1    |

|            | Cockpit layouts                                    | 11   |

|            | Multiple-choice questions                          | 13   |

| Chapter 2  | Number systems                                     | 16   |

| 2.1        | Decimal (denary) numbers                           | 16   |

| 2.2        | Binary numbers                                     | 17   |

| 2.3        | Octal numbers                                      | 19   |

| 2.4        | Hexadecimal numbers                                | 21   |

| 2.5        | American Standard Code for Information Interchange | 23   |

| 2.6        | Multiple-choice questions                          | 28   |

| Chapter 3  | Data conversion                                    | 30   |

| 3.1        | Analogue and digital signals                       | 30   |

| 3.2        | Digital to analogue conversion                     | 31   |

| 3.3        | Analogue to digital conversion                     | 34   |

| 3.4        | Multiple-choice questions                          | 38   |

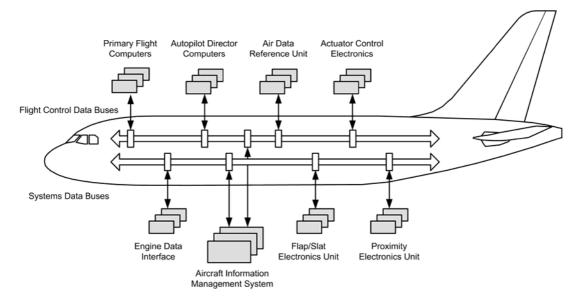

| Chapter 4  | Data buses                                         | 40   |

| 4.1        | Introducing bus systems                            | 41   |

| 4.2        | ARINC 429                                          | 44   |

| 4.3        | Other bus standards                                | 49   |

| 4.4        | Multiple-choice questions                          | 51   |

| Chapter 5  | Logic circuits                                     | 53   |

| -          | Introducing logic                                  | 53   |

|            | Logic circuits                                     | 54   |

|            | Boolean algebra                                    | 55   |

|            | Combinational logic                                | 56   |

#### vi CONTENTS

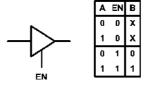

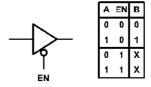

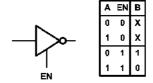

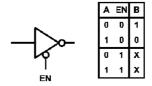

| 5.5        | Tri-state logic                            | 60  |

|------------|--------------------------------------------|-----|

| 5.6        | Monostables                                | 60  |

| 5.7        | Bistables                                  | 62  |

| 5.8        | Logic families                             | 65  |

| 5.9        | Multiple-choice questions                  | 69  |

| Chapter 6  | Computers                                  | 70  |

| 6.1        | Computer systems                           | 70  |

| 6.2        | Data representation                        | 71  |

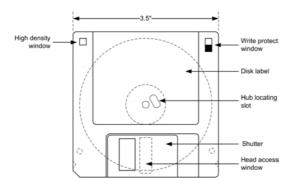

| 6.3        | Data storage                               | 72  |

| 6.4        | Programs and software                      | 78  |

| 6.5        | Backplane bus systems                      | 81  |

| 6.6        | Some examples of aircraft computer systems | 82  |

| 6.7        | Multiple-choice questions                  | 84  |

| Chapter 7  |                                            | 87  |

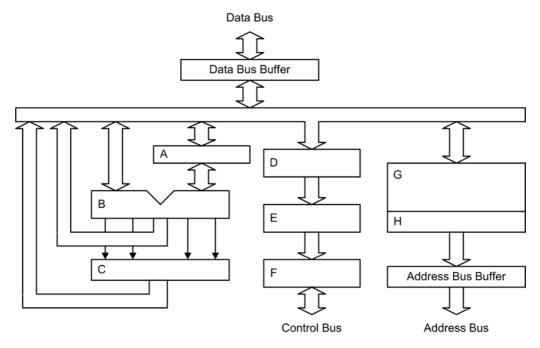

| 7.1        | Internal architecture                      | 87  |

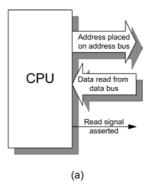

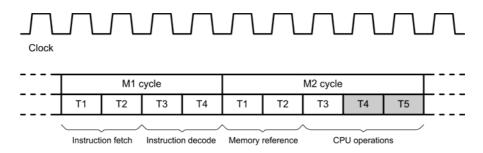

| 7.2        | Microprocessor operation                   | 92  |

| 7.3        | Intel x86 family                           | 94  |

| 7.4        | The Intel Pentium family                   | 99  |

|            | AMD 29050                                  | 100 |

| 7.6        | Multiple-choice questions                  | 102 |

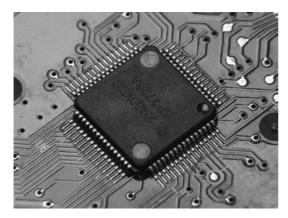

| Chapter 8  | Integrated circuits                        | 105 |

| 8.1        | Scale of integration                       | 106 |

| 8.2        | Fabrication technology                     | 106 |

| 8.3        | .3 Packaging and pin numbering             |     |

| 8.4        | Multiple-choice questions                  | 109 |

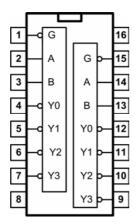

| Chapter 9  | MSI logic                                  | 112 |

| 9.1        | Fan-in and fan-out                         | 112 |

| 9.2        | Coding systems                             | 113 |

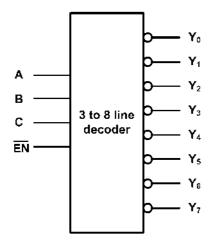

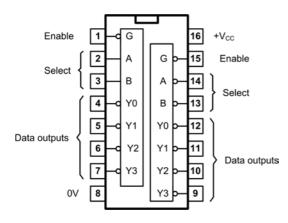

| 9.3        | Decoders                                   | 115 |

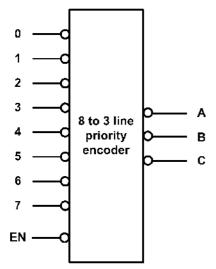

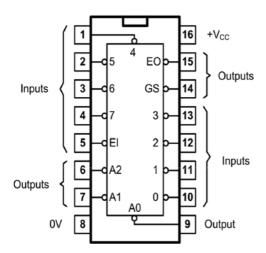

|            | Encoders                                   | 117 |

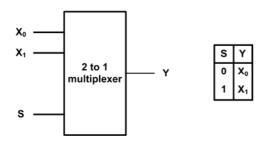

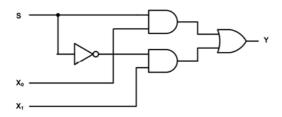

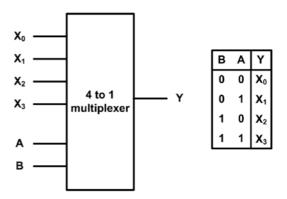

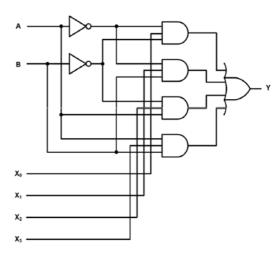

| 9.5        | Multiplexers                               | 119 |

| 9.6        | Multiple-choice questions                  | 121 |

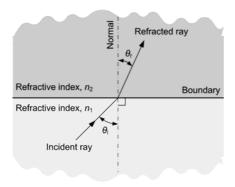

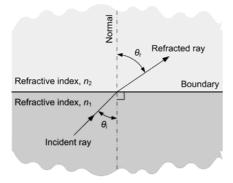

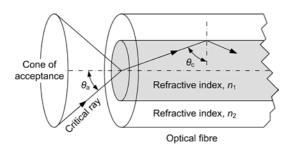

| •          | Fibre optics                               | 123 |

|            | Advantages and disadvantages               | 123 |

|            | Propagation in optical fibres              | 123 |

|            | Dispersion and bandwidth                   | 126 |

|            | Practical optical networks                 | 127 |

|            | Optical network components                 | 129 |

| 10.6       | Multiple-choice questions                  | 130 |

| Chapter 11 | Displays                                   | 132 |

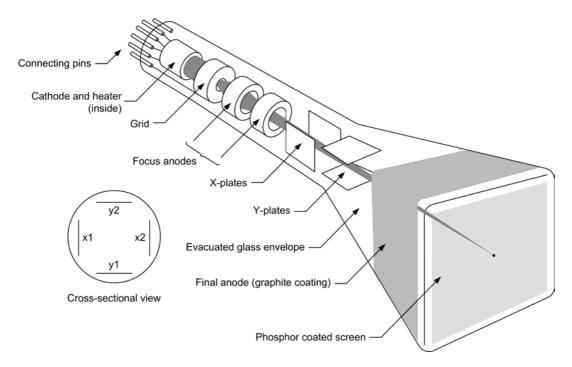

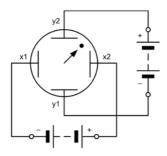

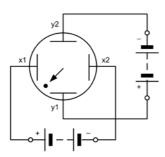

| 11.1       | CRT displays                               | 133 |

|            | Light emitting diodes                      | 139 |

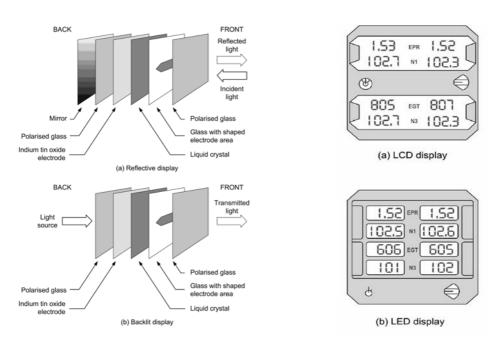

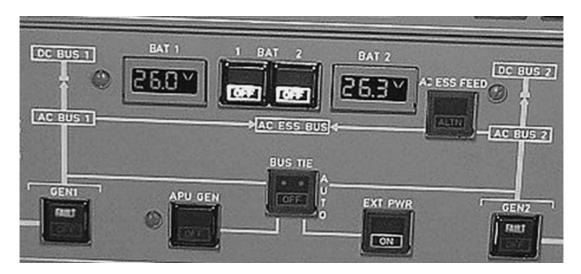

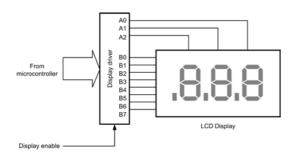

|            | Liquid crystal displays                    | 141 |

| 11.4       | Multiple-choice questions                  | 144 |

| CONTENTS | vii |

|----------|-----|

|          |     |

| Chapter 12 | ESD                                                    | 146 |

|------------|--------------------------------------------------------|-----|

| 12.1       | Static electricity                                     | 146 |

| 12.2       | Static-sensitive devices                               | 148 |

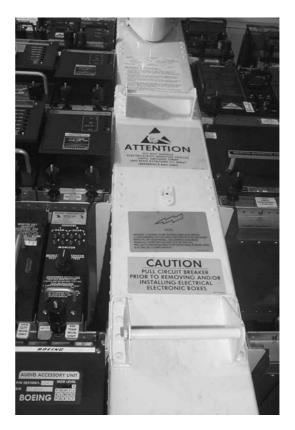

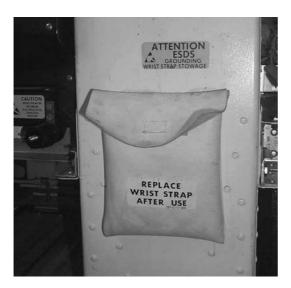

| 12.3       | ESD warnings                                           | 149 |

| 12.4       | Handling and transporting ESDs                         | 150 |

|            | Multiple-choice questions                              | 151 |

| Chapter 13 | Software                                               | 153 |

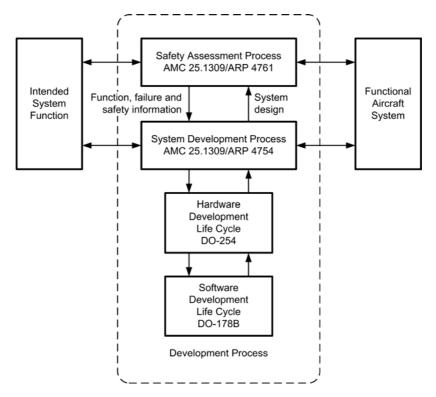

| 13.1       | Software classification                                | 153 |

| 13.2       | Software certification                                 | 154 |

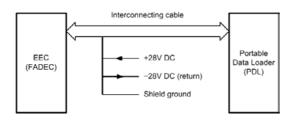

| 13.3       | Software upgrading                                     | 155 |

| 13.4       | Data verification                                      | 160 |

| 13.5       | Multiple-choice questions                              | 160 |

| Chapter 14 | EMC                                                    | 162 |

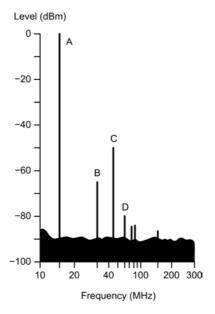

| 14.1       | EMI generation                                         | 162 |

| 14.2       | EMC and avionic equipment                              | 165 |

| 14.3       | Spectrum analysis                                      | 166 |

| 14.4       | Effects and causes of EMI                              | 169 |

| 14.5       | Aircraft wiring and cabling                            | 172 |

| 14.6       | Grounding and bonding                                  | 172 |

| 14.7       | Multiple-choice questions                              | 173 |

| Chapter 15 | Avionic systems                                        | 175 |

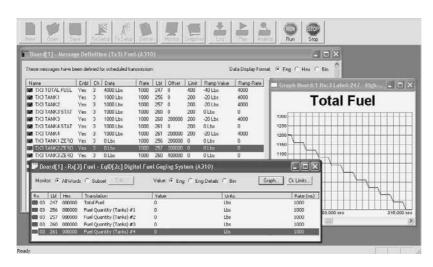

| 15.1       | Aircraft Communication Addressing and Reporting System | 175 |

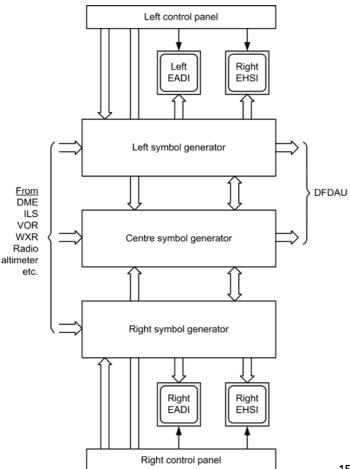

| 15.2       | EFIS                                                   | 176 |

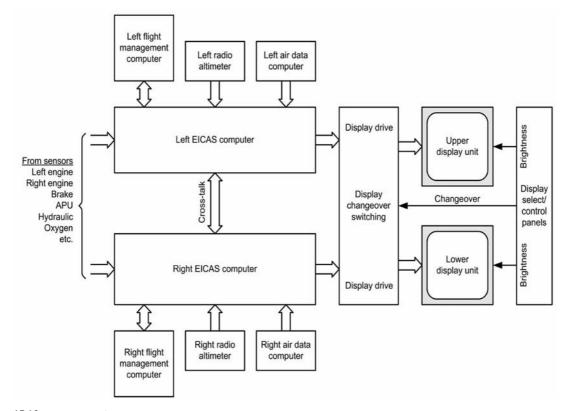

| 15.3       | Engine indication and crew alerting system             | 180 |

| 15.4       | Fly-by-wire                                            | 182 |

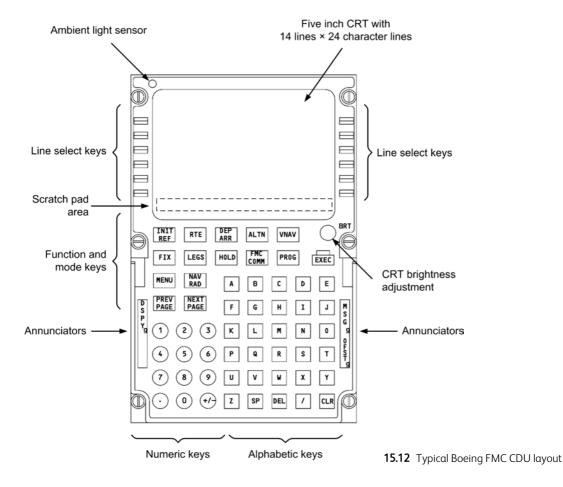

| 15.5       | Flight management system                               | 183 |

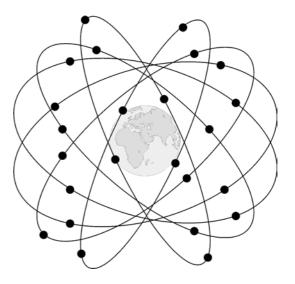

|            | Global Positioning System                              | 184 |

| 15.7       | Inertial reference system                              | 186 |

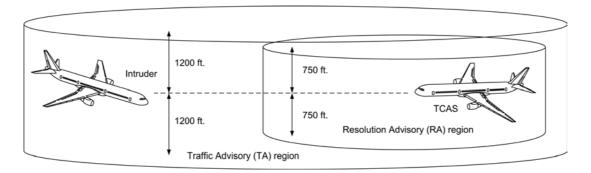

| 15.8       | Traffic alert collision avoidance system               | 187 |

| 15.9       | Automatic test equipment                               | 189 |

|            | Built-in test equipment                                | 189 |

| 15.11      | Multiple-choice questions                              | 189 |

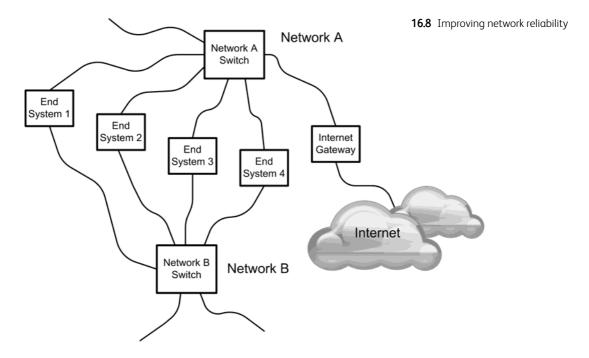

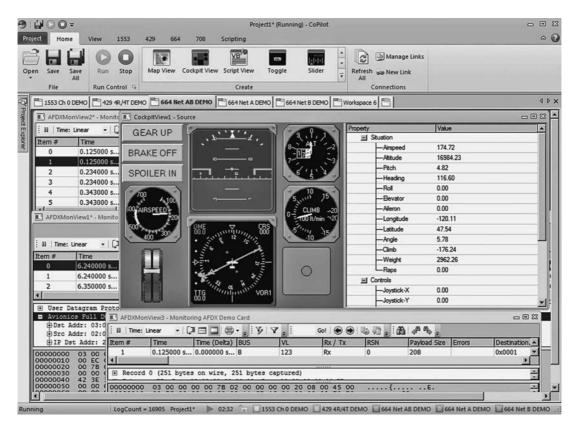

| Chapter 16 | Aircraft data networks and AFDX                        | 191 |

| 16.1       | Integrated modular avionics                            | 191 |

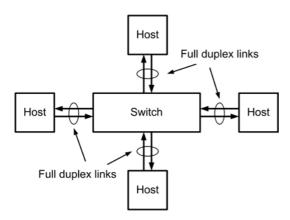

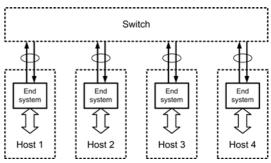

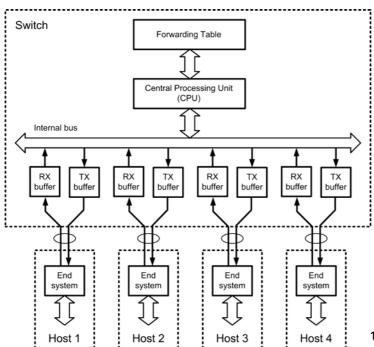

| 16.2       | Local area networks                                    | 191 |

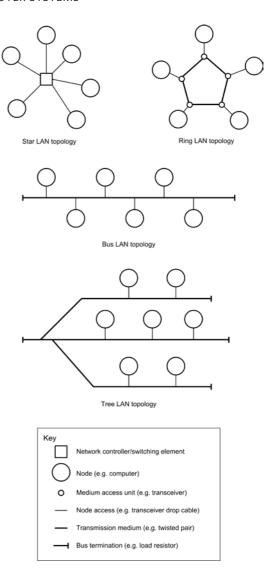

| 16.3       | LAN topology                                           | 192 |

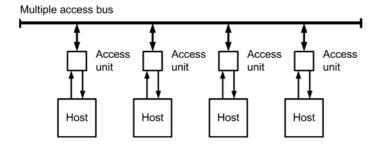

| 16.4       | Ethernet                                               | 193 |

| 16.5       | Avionics full-duplex switched networks                 | 194 |

|            | Determinism and quality of service                     | 195 |

| 16.7       | Virtual links                                          | 196 |

| 16.8       | Bandwidth allocation                                   | 197 |

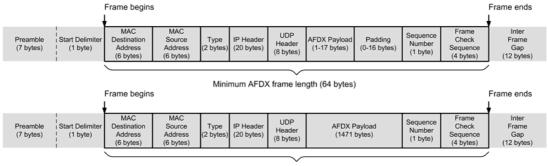

| 16.9       | AFDX frame format                                      | 197 |

| 16.10      | Redundancy, reliability and integrity checking         | 198 |

| 16.11      | Multiple-choice questions                              | 201 |

#### viii CONTENTS

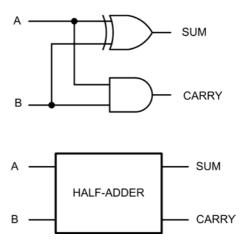

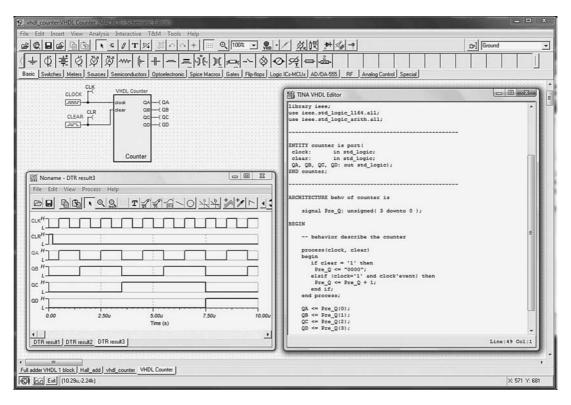

| Chapter 17 | Large-scale logic systems and VHDL          | 203 |

|------------|---------------------------------------------|-----|

| 17.1       | The need for hardware description languages | 203 |

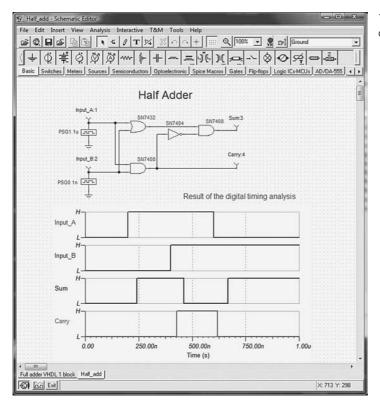

| 17.2       | Entities and entity declarations            | 204 |

| 17.3       | Behavioural declarations                    | 205 |

| 17.4       | VHDL design flow                            | 206 |

| 17.5       | VHDL program structure                      | 207 |

| 17.6       | VHDL signal modes and types                 | 207 |

| 17.7       | VHDL operators                              | 208 |

| 17.8       | Logic decisions and program flow            | 209 |

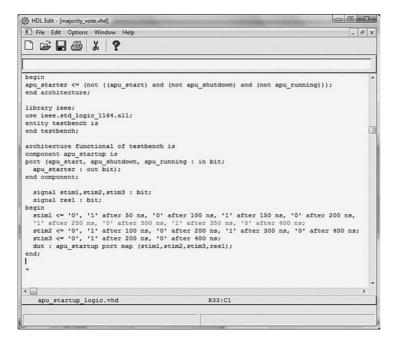

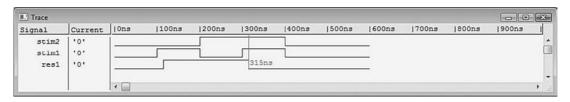

| 17.9       | Simulation and the test bench               | 210 |

| 17.10      | Timing                                      | 212 |

| 17.11      | Multiple-choice questions                   | 214 |

| Appendix 1 | Abbreviations and acronyms                  | 216 |

|            | Revision papers                             | 223 |

| Appendix 3 |                                             | 236 |

|            | Serial data communications: RS-232          | 241 |

| Index      |                                             | 245 |

## Preface

The books in this series have been designed for both independent and tutor-assisted studies. They are particularly useful to the 'self-starter' and to those wishing to update or upgrade their aircraft maintenance licence. The series also provides a useful source of reference for those taking *ab initio* training programmes in EASA Part 147 and FAR 147 approved organizations, as well as those following related programmes in further and higher education institutions.

This book is designed to cover the essential knowledge base required by certifying mechanics, technicians and engineers engaged in engineering maintenance activities on commercial aircraft. In addition, this book should appeal to members of the armed forces and others attending training and educational establishments engaged in aircraft maintenance and related aeronautical engineering programmes (including BTEC National and Higher National units as well as City and Guilds and NVQ courses).

The book provides an introduction to the principles, operation and maintenance of aircraft digital electronic and computer systems. The aim has been to make the subject material accessible and present it in a form that can be readily assimilated. The book provides full syllabus coverage of Module 5 of the EASA Part-66 syllabus, with partial coverage of avionic topics in Modules 11 and 13. The book assumes a basic understanding of aircraft flight controls as well as an appreciation of electricity and electronics (broadly equivalent to Modules 3 and 4 of the EASA Part-66 syllabus).

Chapter 1 sets the scene by providing an overview of flight instruments and cockpit layouts. It also

introduces the use of electronic flight instruments (EFIS) and the displays that they produce.

Denary, binary and hexadecimal number systems are introduced in Chapter 2. This chapter provides numerous examples of the techniques used for converting from one number system to another — for example, binary to hexadecimal or octal to binary.

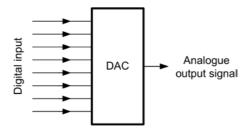

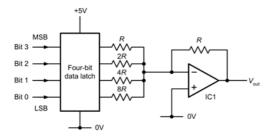

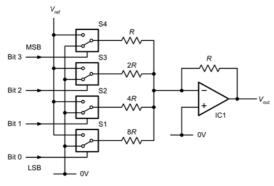

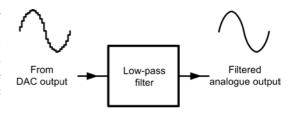

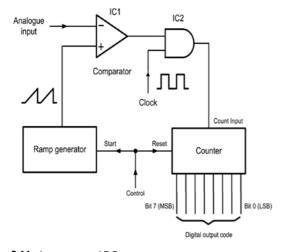

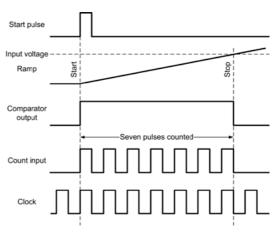

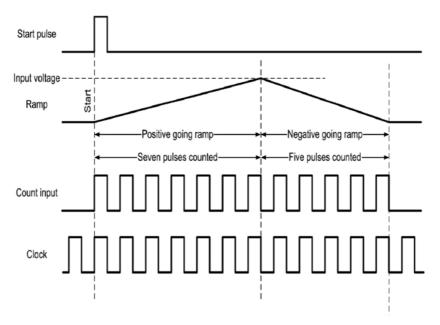

Data conversion is the subject of Chapter 3. This chapter introduces analogue and digital signals and the techniques used for analogue to digital and digital to analogue conversion. Representative circuits are provided for various types of converter, including successive approximation, flash and dual slope analogue to digital converters.

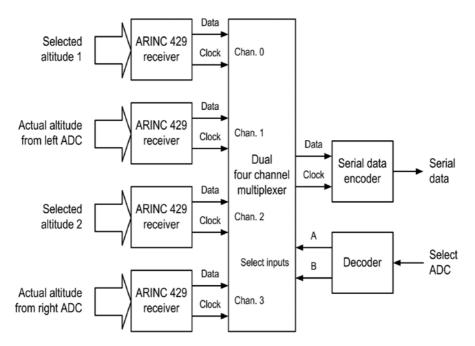

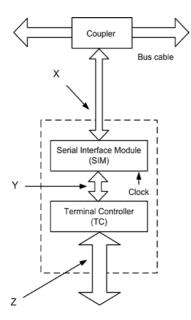

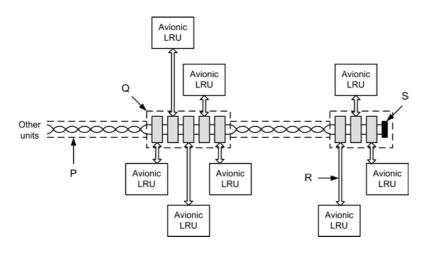

Chapter 4 describes the data bus systems that allow a wide variety of avionic equipment to communicate with one another and exchange data. The principles of aircraft bus systems and architecture are discussed and the operation of the ARINC 429 bus is discussed in detail. Various other bus standards (e.g. ARINC 629 and ARINC 573) are briefly discussed. Further references to aircraft bus systems (including those based on optical fibres) appear in later chapters.

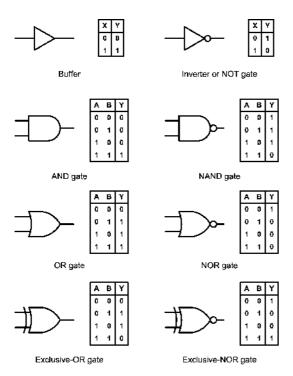

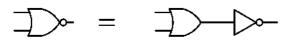

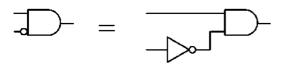

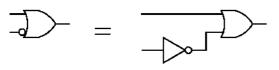

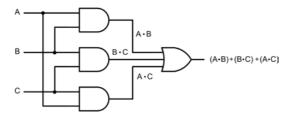

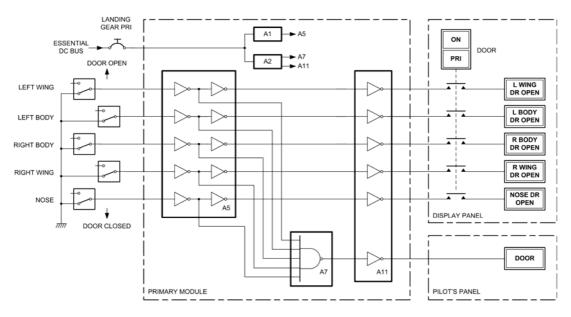

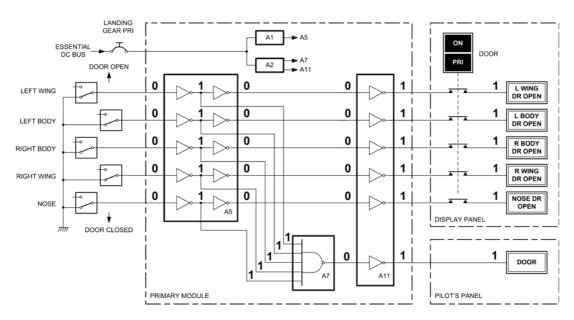

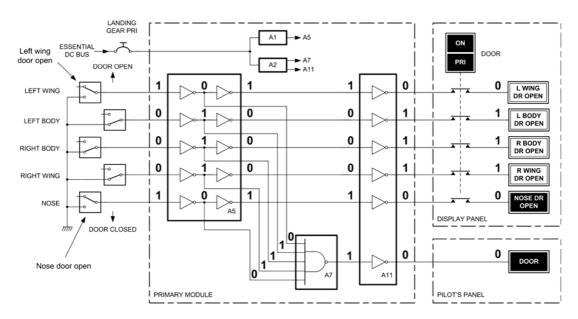

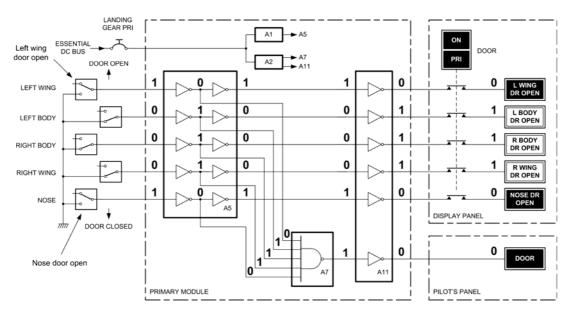

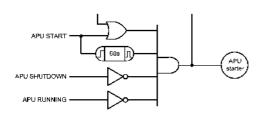

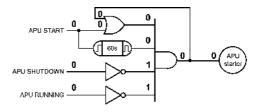

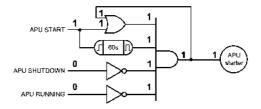

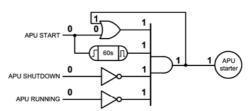

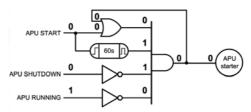

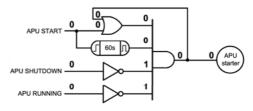

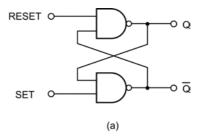

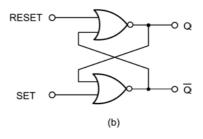

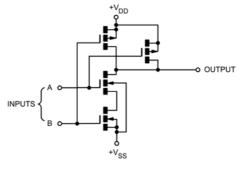

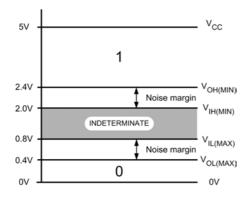

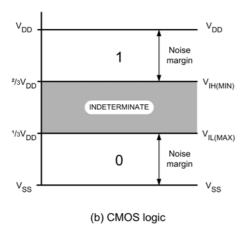

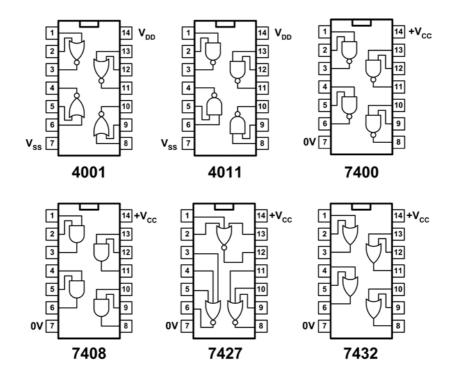

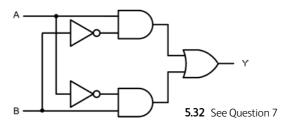

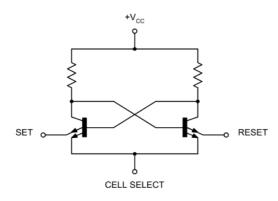

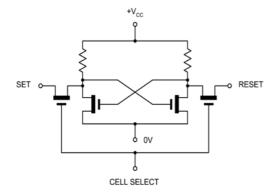

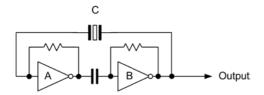

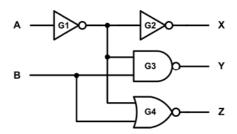

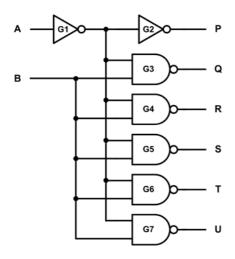

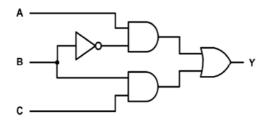

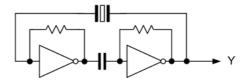

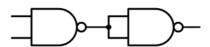

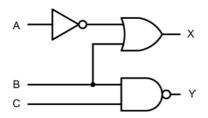

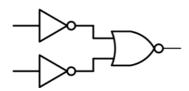

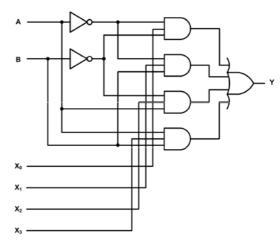

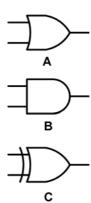

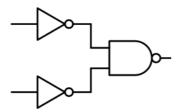

Logic circuits are introduced in Chapter 5. This chapter begins by introducing the basic logic functions (AND, OR, NAND and NOR) before moving on to provide an introduction to Boolean algebra and combinational logic arrangements. An example of the use of combinational logic is given in the form of a landing gear door warning system. Chapter 5 also describes the use of tri-state logic devices as well as monostable and bistable devices. An example of the use of combinational logic is included in the form of

an auxiliary power unit (APU) starter control circuit. The chapter concludes with an explanation of the properties and characteristics of common logic families, including major transistor—transistor logic (TTL) variants and complementary metal oxide semiconductor (CMOS) logic.

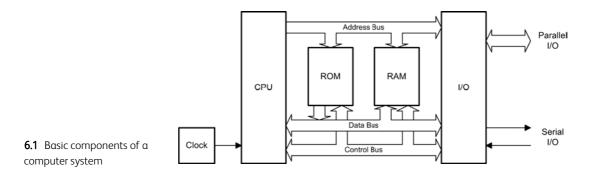

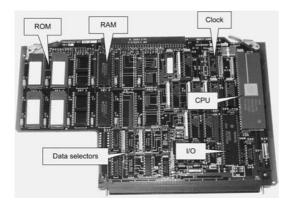

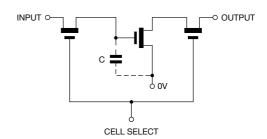

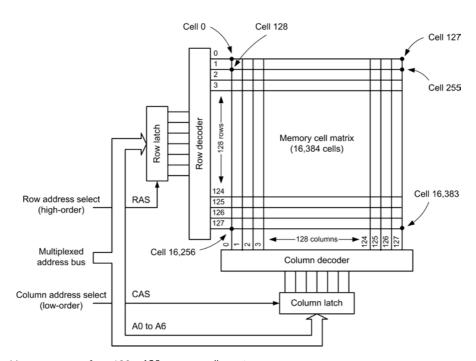

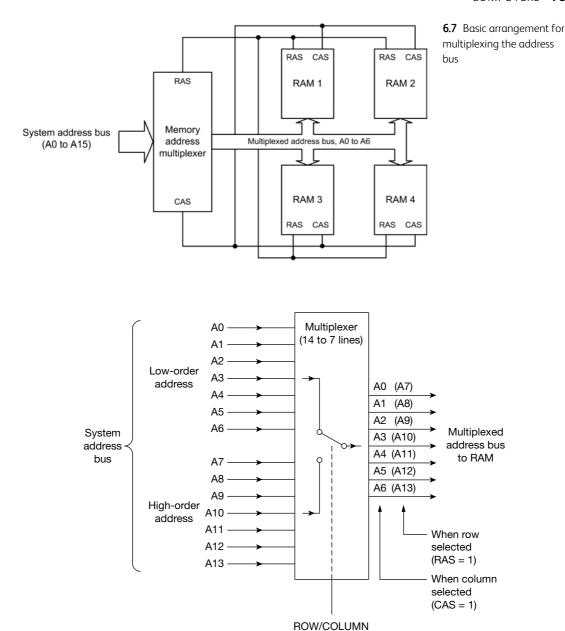

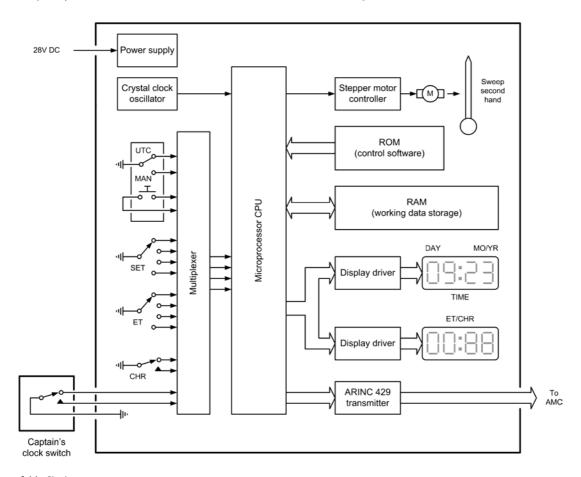

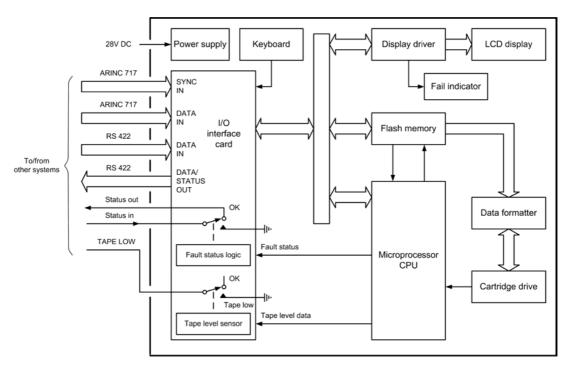

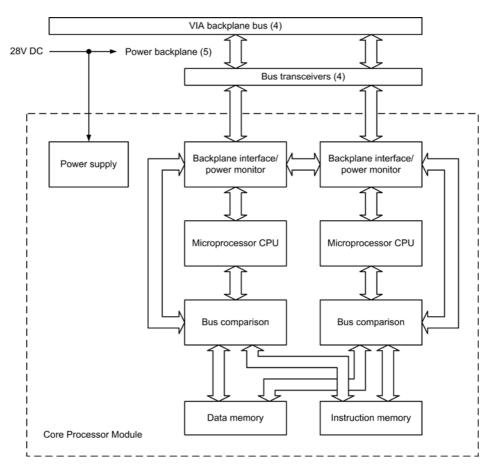

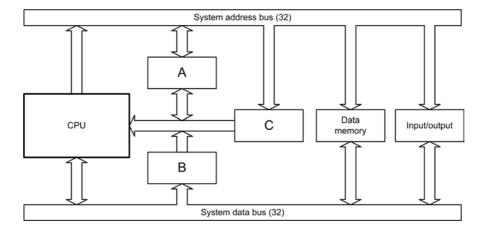

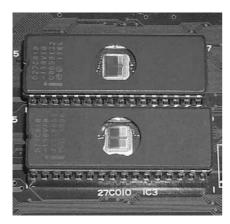

Modern aircraft use increasingly sophisticated avionic systems based on computers. Chapter 6 describes the basic elements used in a computer system and explains how data is represented and stored within a computer system. Various types of semiconductor memory are explained, including random access memory (RAM) and read-only memory (ROM). The chapter also provides an introduction to computer programs and software and examples of computer instructions are given. Chapter 6 also provides an introduction to the backplane bus systems used for larger aircraft computers. The chapter is brought to a conclusion with a discussion of two examples of aircraft computers; a flight deck clock computer and an aircraft integrated data system (AIDS) data recorder.

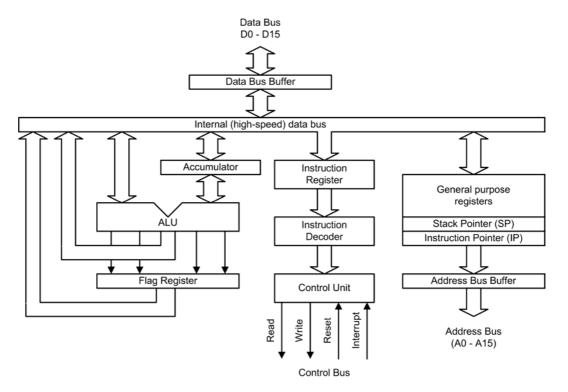

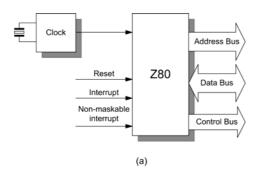

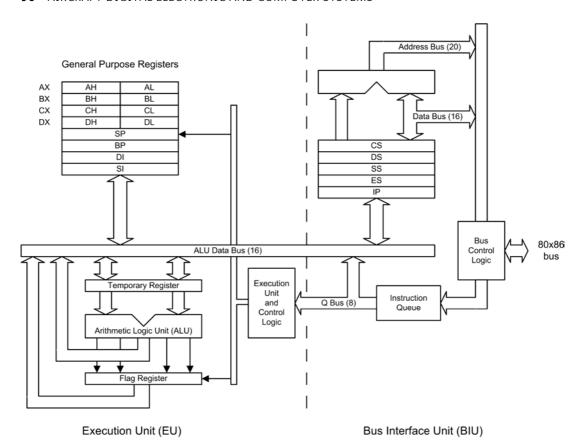

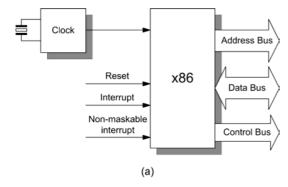

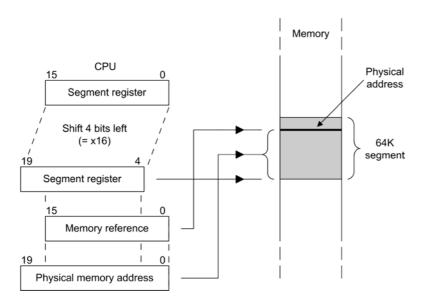

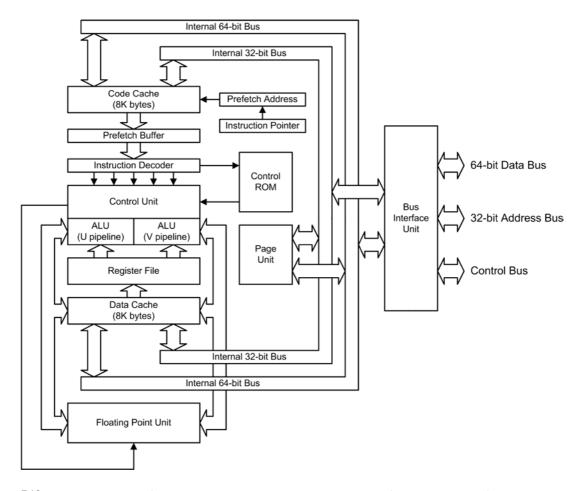

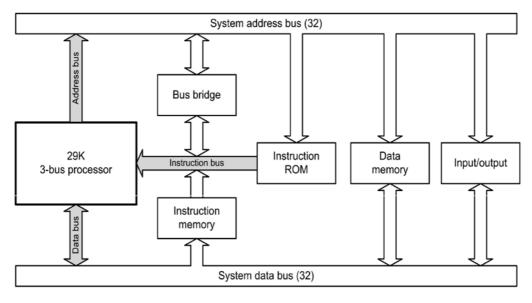

Chapter 7 provides an introduction to the operation of microprocessor central processing units (CPU). The internal architecture of a typical CPU is presented, together with a detailed explanation of its operation and the function of its internal elements.

Examples of several common microprocessor types are given, including the Intel x86 family, Intel Pentium family and the AMD 29050, which now forms the core of a proprietary Honeywell application-specific integrated circuit (ASIC) specifically designed for critical embedded aerospace applications.

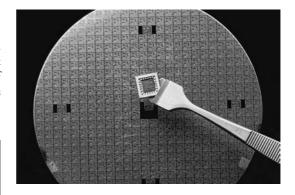

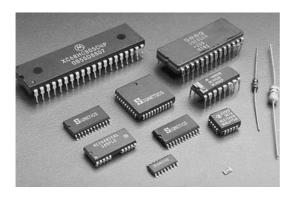

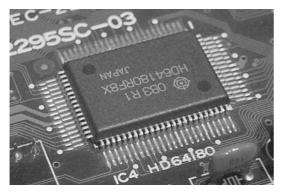

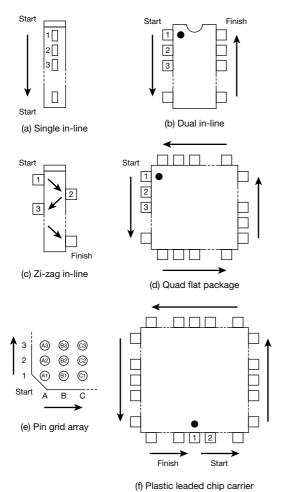

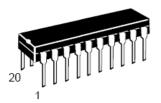

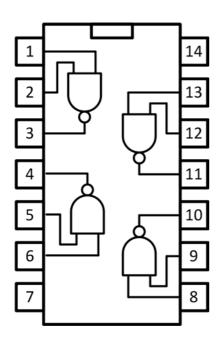

Chapter 8 describes the fabrication technology and application of a wide variety of modern integrated circuits, from those that use less than ten to those with many millions of active devices. The chapter also includes sections on the packaging and pin numbering of integrated circuit devices.

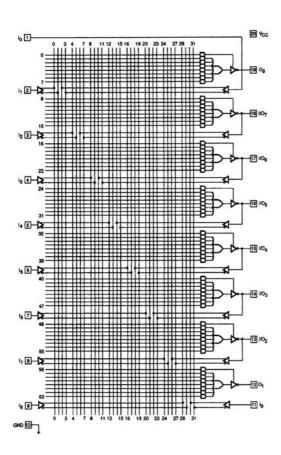

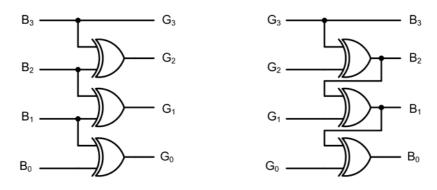

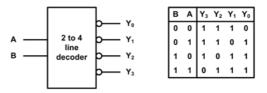

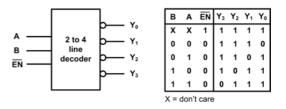

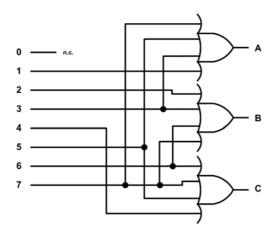

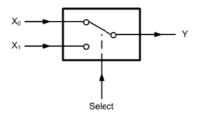

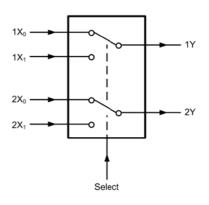

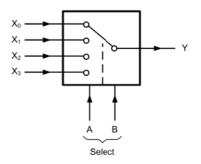

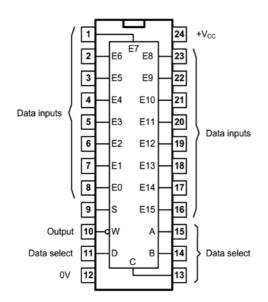

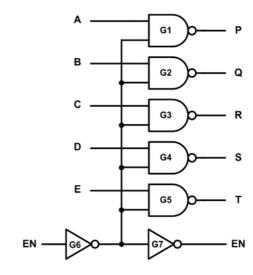

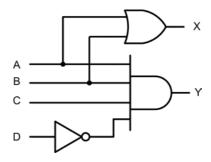

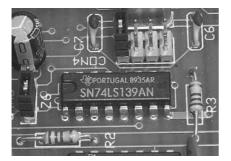

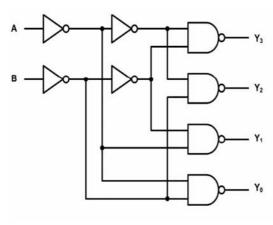

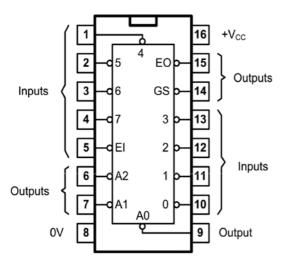

Medium-scale integrated (MSI) logic circuits are frequently used in aircraft digital systems to satisfy the need for more complex logic functions, such as those used for address decoding, code conversion and the switching of logic signals between different bus systems. Chapter 9 describes typical MSI devices and their applications (including decoding, encoding and multiplexing). Examples of several common MSITTL devices are included.

By virtue of their light weight, compact size, exceptional bandwidth and high immunity to electromagnetic interference, optical fibres are now widely used to interconnect aircraft computer systems. Chapter 10 provides an introduction to optical fibres and their increasing use in the local area networks (LANs) used in aircraft.

Chapter 11 describes typical displays used in avionic systems, including the cathode ray tube (CRT) and active matrix liquid crystal displays (AMLCD) used in electronic flight instrument systems (EFIS).

Modern microelectronic devices are particularly susceptible to damage from stray static charges and, as a consequence, they require special handling precautions. Chapter 12 deals with the techniques and correct practice for handling and transporting such devices.

Aircraft software is something that you can't see and you can't touch, yet it must be treated with the same care and consideration as any other aircraft part. Chapter 13 describes the different classes of software used in an aircraft and explains the need for certification and periodic upgrading or modification. The chapter provides an example of the procedures required for upgrading the software used in an electronic engine control (EEC).

One notable disadvantage of the increasing use of sophisticated electronics within an aircraft is the proliferation of sources of electromagnetic interference (EMI) and the urgent need to ensure that avionic systems are electromagnetically compatible with one another. Chapter 14 provides an introduction to electromagnetic compatibility (EMC) and provides examples of measures that can be taken to both reduce EMI and improve EMC. The chapter also discusses the need to ensure the electrical integrity of the aircraft structure and the techniques used for grounding and bonding, which serves to protect an aircraft (and its occupants) from static and lightning discharge

Chapter 15 provides an overview of a variety of different avionic systems that are based on the use of digital electronics and computer systems. This chapter serves to bring into context the principles and theory discussed in the previous chapters.

The use of integrated modular avionics (IMA) has become commonplace in the latest generation of aircraft. Chapter 16 provides an introduction to the use of ethernet-based networks in modern aircraft. After a brief explanation of the different topologies used in LANs it provides an outline of the architecture and operation of the avionics full-duplex switched network (AFDX).

Finally, Chapter 17 will provide you with an introduction to some of the techniques used in the development, testing and verification of the very large-scale logic systems used in aircraft today. Usually fabricated on a single silicon chip, such systems often comprise many tens or hundreds of thousands of individual logic elements connected in a way that fulfils the requirements of the system. Simple examples of the use of very high-speed integrated circuit hardware description language (VHDL) are included in this chapter, sufficient to provide engineers with an understanding of how the language contributes to the development process.

The book concludes with four useful appendices, including a comprehensive list of abbreviations and acronyms used with aircraft digital electronics and computer systems.

The review questions at the end of each chapter are typical of those used in CAA and other examinations. Further examination practice can be gained from the six revision papers given in Appendix 2. Other features that will be particularly useful if you are an independent learner are the 'key points' and 'test your understanding' questions interspersed throughout the text.

This page intentionally left blank

## **Acknowledgements**

The author would like to express sincere thanks to those who helped in producing this book. In particular, thanks go to Gavin Fidler and Emma Gadsden from Taylor & Francis who ably 'fielded' my many queries and who supported the book from its inception. Lloyd Dingle (who had the original idea for this series) for his vision and tireless enthusiasm. David Wyatt for proofreading the original manuscript and

for acting as a valuable 'sounding board'. Finally, a big 'thank you' to Yvonne for her patience, understanding and support during the many late nights and early mornings that went into producing it!

Supporting material for this book (including interactive questions and answers) is available online. To access this material please go to www.66web.co.uk and follow the instructions on screen.

This page intentionally left blank

### 1 Introduction

Although it may not be apparent at first sight, it's fair to say that a modern aircraft simply could not fly without the electronic systems that provide the crew with a means of controlling the aircraft. Avionic systems are used in a wide variety of different applications, ranging from flight control and instrumentation to navigation and communication. In fact, an aircraft that uses modern 'fly-by-wire' techniques could not even get off the ground without the electronic systems that make it work.

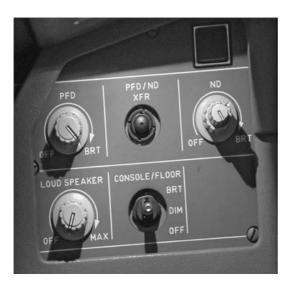

This chapter begins with an introduction to the basic instruments needed for indicating parameters such as heading, altitude and airspeed, and then continues by looking at their modern electronic equivalents. Finally, we show how flight information can be combined using integrated instrument systems and flight information displays, as shown in Figure 1.1.

#### 1.1 FLIGHT INSTRUMENTS

Of paramount importance in any aircraft is the system (or systems) used for sensing and indicating the aircraft's attitude, heading, altitude and speed. In early aircraft, these instruments were simple electromechanical devices. Indeed, when flying under visual flight rules (VFR) rather than instrument flight rules (IFR) the pilot's most important source of information about what the aircraft was doing would have been the view out of the cockpit window! Nowadays, sophisticated avionic and display technology, augmented by digital logic and computer systems, has made it possible for an aircraft to be flown (with a few

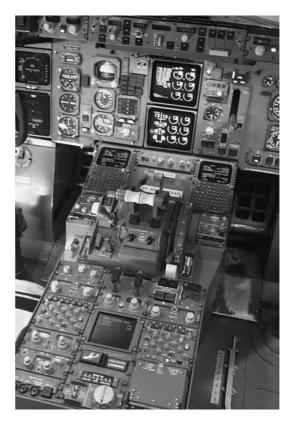

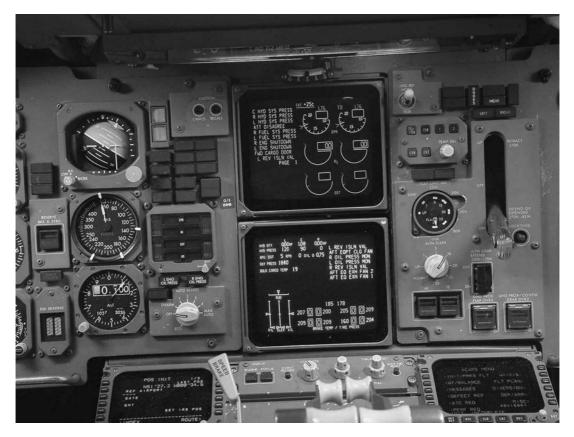

1.1 Boeing 757 flight instruments and displays

possible exceptions) entirely by reference to instruments. More about these important topics appears in Chapters 5 and 6.

#### 2 AIRCRAFT DIGITAL ELECTRONIC AND COMPUTER SYSTEMS

Various instruments are used to provide the pilot with flight-related information, such as the aircraft's current heading, airspeed and attitude.

Modern aircraft use electronic transducers and electronic displays and indicators. Cathode ray tubes (CRT) and liquid crystal displays (LCD) are increasingly used to display this information in what has become known as a 'glass cockpit'. Modern passenger aircraft generally have a number of such displays, including those used for primary flight data and multifunction displays that can be configured to display a variety of information. We shall begin this section with a brief review of the basic flight instruments.

#### 1.1.1 Basic flight instruments

Crucial among the flight instruments fitted to any aircraft are those that indicate the position and attitude of the aircraft. These basic flight instruments are required to display information concerning:

- · heading

- altitude

- airspeed

- rate of turn

- rate of climb (or descent)

- attitude (relative to the horizon).

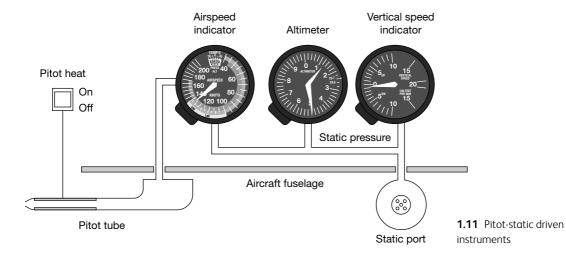

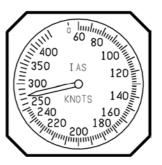

A summary of the instruments that provide these indications is shown in Table 1.1, with the typical instrument displays shown in Figures 1.2–1.8. Note that several of these instruments are driven from the aircraft's pitot-static system. Because of this, they are often referred to as 'air data instruments' (see Figures 1.11–1.13).

1.3 Standby Altimeter

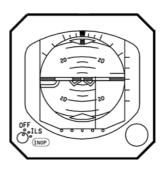

1.4 Attitude indicator

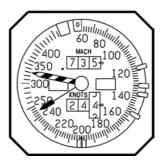

1.5 Airspeed indicator

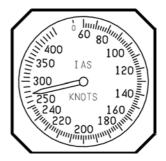

**1.6** Standby airspeed indicator

1.2 Altimeter

**Table 1.1** Basic flight instruments

| Instrument                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Altimeter (Figure 1.2)                                        | Indicates the aircraft's height (in feet or metres) above a reference level (usually mean sea level) by measuring the local air pressure. To provide accurate readings the instrument is adjustable for local barometric pressure. In large aircraft a second standby altimeter is often available (see Figure 1.3)                                                                                                                                                                                |

| Attitude indicator or<br>'artificial horizon'<br>(Figure 1.4) | Displays the aircraft's attitude relative to the horizon (see Figure 1.4). From this the pilot can tell whether the wings are level and if the aircraft nose is pointing above or below the horizon. This is a primary indicator for instrument flight and is also useful in conditions of poor visibility. Pilots are trained to use other instruments in combination should this instrument or its power fail                                                                                    |

| Airspeed indicator<br>(Figures 1.5 and 1.6)                   | Displays the speed of the aircraft (in knots) relative to the surrounding air. The instrument compares the ram-air pressure in the aircraft's pitot-tube with the static pressure (see Figure 1.11). The indicated airspeed must be corrected for air density (which varies with altitude, temperature and humidity) and for wind conditions in order to obtain the speed over the ground                                                                                                          |

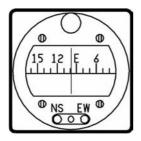

| Magnetic compass<br>(Figure 1.7)                              | Indicates the aircraft's heading relative to magnetic north. However, due to the inclination of the earth's magnetic field, the instrument can be unreliable when turning, climbing, descending or accelerating. Because of this the HSI (see below) is used. For accurate navigation, it is necessary to correct the direction indicated in order to obtain the direction of true north or south (at the extreme ends of the Earth's axis of rotation)                                            |

| Horizontal situation indicator                                | The horizontal situation indicator (HSI) displays a plan view of the aircraft's position showing its heading. Information used by the HSI is derived from the compass and radio navigation equipment (VOR), which provides accurate bearings using ground stations. In light aircraft the VOR receiver is often combined with the VHF communication radio equipment but in larger aircraft a separate VOR receiver is fitted                                                                       |

| Turn and bank indicator or 'turn coordinator'                 | Indicates the direction and rate of turn. An internally mounted inclinometer displays the 'quality' of turn, i.e. whether the turn is correctly coordinated, as opposed to an uncoordinated turn in which the aircraft would be in either a slip or skid. In modern aircraft the turn and bank indicator has been replaced by the turn coordinator which displays (a) rate and direction of roll when the aircraft is rolling, and (b) rate and direction of turn when the aircraft is not rolling |

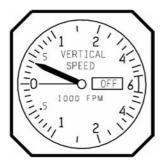

| Vertical speed indicator<br>(Figure 1.8)                      | Indicates rate of climb or descent (in feet per minute or metres per second) by sensing changes in air pressure (see Figure 1.11)                                                                                                                                                                                                                                                                                                                                                                  |

#### 4 AIRCRAFT DIGITAL ELECTRONIC AND COMPUTER SYSTEMS

**1.7** Standby magnetic compass

1.8 Standby vertical speed indicator

#### **TEST YOUR UNDERSTANDING 1.1**

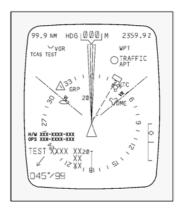

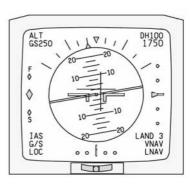

Identify the instruments shown in Figs.1.9 and 1.10. Also state the current indication displayed by each instrument.

**1.9** See Test your understanding 1.1

**1.10** See Test your understanding 1.1

1.12 An aircraft static port

1.13 A pitot tube (upper right) and an angle-of-attack sensor (lower left)

#### 1.1.2 Acronyms

A number of acronyms are used to refer to flight instruments and cockpit indicating systems. Unfortunately, there is also some variation in the acronyms used by different aircraft manufacturers. The most commonly used acronyms are listed in Table 1.2. A full list can be found in Appendix 1.

#### **TEST YOUR UNDERSTANDING 1.2**

What do the following acronyms stand for?

1. VFR 2. CRT 4. ADI

5. PFD.

3. LCD

**Table 1.2** Some commonly used acronyms

| Acronym | Meaning                                     |

|---------|---------------------------------------------|

| ADI     | Attitude direction indicator                |

| ASI     | Airspeed indicator                          |

| CDU     | Control and display unit                    |

| EADI    | Electronic attitude and direction indicator |

| ECAM    | Electronic centralised aircraft monitoring  |

| EFIS    | Electronic flight instrument system         |

| EHSI    | Electronic horizontal situation indicator   |

| EICAS   | Engine indicating and crew alerting system  |

| FDS     | Flight director system                      |

| FIS     | Flight instrument system                    |

| FMC     | Flight management computer                  |

| FMS     | Flight management system                    |

| HSI     | Horizontal situation indicator              |

| IRS     | Inertial reference system                   |

| ND      | Navigation display                          |

| PFD     | Primary flight display                      |

| RCDI    | Rate of climb/descent indicator             |

| RMI     | Radio magnetic indicator                    |

| VOR     | Very high frequency omni-range              |

| VSI     | Vertical speed indicator                    |

#### 1.1.3 Electronic flight instruments

Modern aircraft make extensive use of electronic instruments and displays. One advantage of using electronic instruments is that data can easily be exchanged between different instrument systems and used as a basis for automatic flight control. We will explore the potential of this a little later in this chapter but, for now, we will look at the two arguably most important electronic instruments, the electronic attitude and direction indicator (EADI) and the electronic horizontal situation indicator (EHSI).

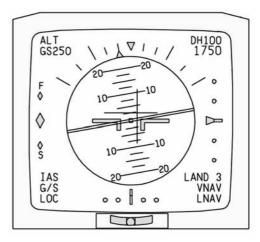

#### Electronic attitude and direction indicator

The electronic attitude direction indicator (EADI – see Figure 1.14) is designed to replace the basic ADI and normally comprises:

- an attitude indicator

- a fixed aircraft symbol

- · pitch and bank command bars

- a glide slope indicator

- a localiser deviation indicator

- a slip indicator

- · flight mode annunciator

- · various warning flags.

The aircraft's attitude relative to the horizon is indicated by the fixed aircraft symbol and the flight command bars. The pilot can adjust the symbol to one of three flight modes. To fly the aircraft with the command bars armed, the pilot simply inserts the aircraft symbol between the command bars.

The command bars move up for a climb or down for descent, roll left or right to provide lateral guidance. They display the computed angle of bank for standard-rate turns to enable the pilot to reach and fly a selected heading or track. The bars also show pitch commands that allow the pilot to capture and fly an

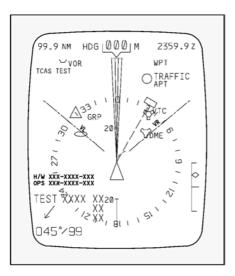

1.14 A typical EADI display

instrument landing system (ILS) glide slope, a preselected pitch attitude or maintain a selected barometric altitude. To comply with the directions indicated by the command bars, the pilot manoeuvres the aircraft to align the fixed symbol with the command bars. When not using the bars, the pilot can move them out of view.

The glide slope deviation pointer represents the centre of the ILS glide slope and displays vertical deviation of the aircraft from the glide slope centre. The glide slope scale centreline shows aircraft position in relation to the glide slope.

The localiser deviation pointer, a symbolic runway, represents the centre of the ILS localiser, and comes into view when the pilot has acquired the glide slope. The expanded scale movement shows lateral deviation from the localiser and is approximately twice as sensitive as the lateral deviation bar in the horizontal situation indicator. The selected flight mode is displayed in the lower left of the EADI for pitch modes, and lower right for lateral modes. The slip indicator provides an indication of slip or skid indications.

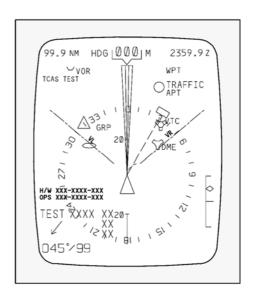

#### Electronic horizontal situation indicator

The electronic horizontal situation indicator (EHSI) assists pilots with the interpretation of information provided by a number of different navigation aids. There are various types of EHSI, but essentially they all perform the same function. An EHSI display (see Figure 1.15) can be configured to display a variety of information (combined in various different ways), including:

- heading indication

- radio magnetic indication (RMI)

- track indication

- range indication

- wind speed and direction

- VOR, DME, ILS or ADF information.

#### 1.1.4 Flight director systems

The major components of a flight director system (FDS) are the EADI and EHSI, working together with a mode selector and a flight director computer.

The FDS combines the outputs of the electronic flight instruments to provide an easily interpreted

#### **1.15** A typical EHSI display

display of the aircraft's flight path. By comparing this information with the pre-programmed flight path, the system can automatically compute the necessary flight control commands to obtain and hold the desired

The flight director system receives information from the:

- attitude gyro

- VOR/localiser/glide slope receiver

- radar altimeter

- compass system

- barometric sensors.

The flight director computer uses this data to provide flight control command information that enables the aircraft to:

- fly a selected heading

- fly a predetermined pitch attitude

- maintain altitude

- intercept a selected VOR track and maintain that track

- fly an ILS glide slope/localiser.

The flight director control panel comprises a mode selector switch and control panel that provides the input information used by the FDS.

The pitch command control pre-sets the desired pitch angle of the aircraft for climb or descent. The

command bars on the FDS then display the computed attitude to maintain the pre-selected pitch angle. The pilot may choose from among many modes, including the HDG (heading) mode, the VOR/LOC (localiser tracking) mode, or the AUTO APP or G/S (automatic capture and tracking of ILS and glide path) mode. The auto mode has a fully automatic pitch selection computer that takes into account aircraft performance and wind conditions, and operates once the pilot has reached the ILS glide slope.

Flight director systems have become increasingly more sophisticated in recent years. More information appears in Chapter 15.

#### **TEST YOUR UNDERSTANDING 1.3**

- 1. What are the advantages of flight director systems (FDS)?

- 2. List four inputs used by a basic FDS.

- 3. List four types of flight control information that can be produced by a basic FDS.

- 4. Explain the function of the FDS auto mode during aircraft approach and landing.

- 5. Explain the use of the symbolic runway in relation to the display produced by the EADI.

#### 1.1.5 Electronic flight instrument systems

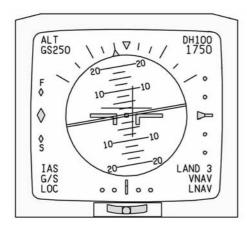

An electronic flight instrument system (EFIS) is a system of graphically presented displays with underlying sensors, electronic circuitry and software that effectively replaces all mechanical flight instruments and gauges with a single unit.

The EFIS fitted to larger aircraft consists of a primary flight display (PFD) or electronic attitude and direction indicator (EADI) and a navigation display (ND) or electronic horizontal situation indicator (EHSI). These instruments are duplicated for the captain and the first officer.

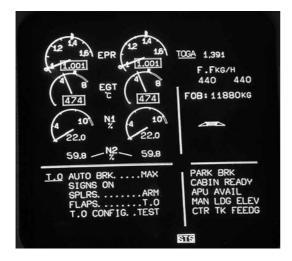

The PFD presents the usual attitude indicator in connection with other data, such as airspeed, altitude, vertical speed, heading or coupled landing systems (see Figure 1.16). The ND displays route information,

1.16 EFIS primary flight display

**1.17** EFIS navigation display

a compass card or the weather radar picture (see Figure 1.17).

In addition to the two large graphical displays, a typical EFIS will have a display select panel, a display processor unit, a weather radar panel, a multi-function processor unit, and a multi-function display. We will look briefly at each of these.

#### EFIS primary flight display

The typical EFIS PFD is a multicolour CRT or LCD display unit that presents a display of aircraft attitude and flight control system commands, including VOR, localiser, TACAN (tactical air navigation), or RNAV (area navigation) deviation, together with glide slope or pre-selected altitude deviation. Various other information can be displayed, including mode annunciation, radar altitude, decision height and excessive ILS deviation.

#### EFIS navigation display

Like the EFIS PFD, a typical EFIS ND takes the form of a multicolour CRT or LCD display unit. However, in this case the display shows the aircraft's horizontal situation information which, according to the display mode selected, can include compass heading, selected heading, selected VOR, localiser or RNAV course and deviation (including annunciation or deviation type), navigation source annunciation, digital selected course/desired track readout, excessive ILS deviation, to/from information, distance to station/waypoint, glide slope, or VNAV deviation, ground speed, timeto-go, elapsed time or wind, course information and source annunciation from a second navigation source, weather radar target alert, waypoint alert when RNAV is the navigation source, and a bearing pointer that can be driven by VOR, RNAV or ADF sources as selected on the display select panel. The display mode can also be set to approach format or en-route format with or without weather radar information included in the display.

#### Display select panel

The display select panel (DSP) provides navigation sensor selection, bearing pointer selection, format selection, navigation data selection (ground speed, time-to-go, time and wind direction/speed), and the selection of VNAV (if the aircraft has this system), weather or second navigation source on the ND. A DH SET control that allows decision height to be set on the PFD is also provided. Additionally, course, course direct to and heading are selected from the DSP.

#### Display processor unit

The display processor unit (DPU) provides sensor input processing and switching, the necessary deflection and video signals and power for the electronic flight displays. The DPU is capable of driving two electronic flight displays with different deflection and video signals. For example, a PFD on one display and an ND on the other.

#### Weather radar panel

The weather radar panel (WXP) provides MODE control (OFF, STBY, TEST, NORM, WX and MAP), RANGE selection (10, 25, 50, 100, 200 and 300 nm) and system operating controls for the display of weather radar information on the MFD and the ND when RDR is selected on the MFD and/or the DSP.

#### Multi-function display

The multi-function display takes the form of another multicolour CRT or active-matrix LCD display unit. The display is normally mounted on the instrument panel in the space provided for the weather radar (WXR) indicator. Standard functions displayed by the unit include weather radar, pictorial navigation map and, in some systems, checklist and other operating data. Additionally, the MFD can display flight data or navigation data in case of a PFD or ND failure.

#### Multifunction processor unit

The multifunction processor unit (MPU) provides sensor input processing and switching and the necessary deflection and video signals for the multifunction display. The MPU can provide the deflection and video signals to the PFD and ND displays in the event of failures in either or both DPUs.

#### 1.1.6 Electronic centralised aircraft monitor

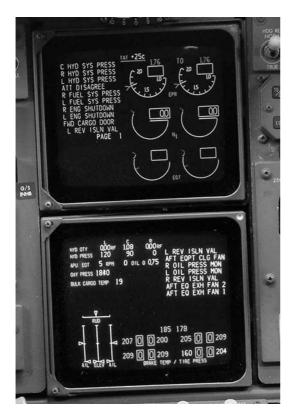

Technical information concerning the state of an Airbus aircraft is displayed using the aircraft's electronic centralised aircraft monitor (ECAM - see

Figure 1.18). This normally takes the form of two CRT or LCD displays that are vertically arranged in the centre of the instrument panel. The upper (primary) display shows the primary engine parameters (N1/fan speed, EGT, N2/high pressure turbine speed), as well as the fuel flow, the status of lift augmentation devices (flap and slat positions), along with other information. The lower (secondary) ECAM display presents additional information, including that relating to any system malfunction and its consequences.

1.18 A320 ECAM displays located above the centre console between the captain and first officer

#### Engine indicating and crew alerting system

In Boeing aircraft the equivalent integrated electronic aircraft monitoring system is known as the engine indicating and crew alerting system (EICAS). This system provides graphical monitoring of the engines of later Boeing aircraft, replacing a large number of individual panel-mounted instruments. In common with the Airbus ECAM system, EICAS uses two vertically mounted, centrally located displays (see Figure 1.19).

#### **TEST YOUR UNDERSTANDING 1.4**

Figure 1.20 shows a flight deck display.

- Identify the display.

- 2. What information is currently displayed?

1.19 Boeing 757 EICAS display

**1.20** See Test your understanding 1.4

- 3. Where is the display usually found?

- What fan speed is indicated?

- 5. What temperature is indicated?

The upper (primary) EICAS display shows the engine parameters and alert messages, while the lower (secondary) display provides supplementary data (including advisory and warning information). We shall be looking at the ECAM and EICAS systems in greater detail later in Chapter 15.

#### 1.1.8 Flight management system

The flight management system (FMS) fitted to a modern passenger aircraft brings together data and information gathered from the electronic flight instruments, aircraft monitoring and navigation systems, and provides outputs that can be used for automatic control of the aircraft from immediately after take-off to final approach and landing. The key elements of an FMS include a flight management computer (FMC), control and display unit (CDU), inertial reference system (IRS), auto flight control system (AFCS) and a system of data buses that facilitates the interchange of data with the other digital and computerised systems and instruments fitted to the aircraft.

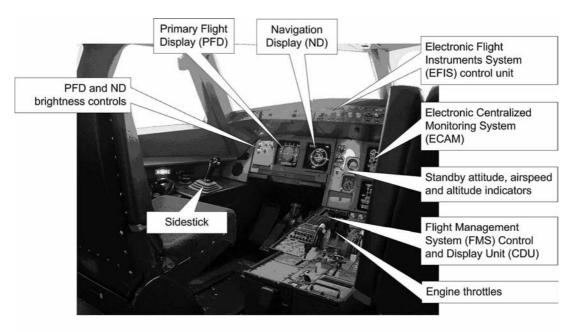

Two FMSs are fitted, one for the captain and one for the first officer. During normal operation the two systems share the incoming data. However, each system can be made to operate independently in the event of failure. By automatically comparing (on a continuous basis) the indications and outputs provided by the two systems it is possible to detect faults within the system and avoid erroneous indications. The inputs to the FMC are derived from several other systems, including IRS, EICAS, engine thrust management computer and the air data computer. Figures 1.21 and 1.22 shows the FMC control and display units fitted to an A320 aircraft. We shall be looking at the operation of the FMS in greater detail later in Chapter 15.

1.21 Captain's FMS CDU

1.22 A320 cockpit layout

#### 1.2 COCKPIT LAYOUTS

Major developments in display technology and the introduction of increasingly sophisticated aircraft computer systems have meant that cockpit layouts have been subject to continuous change over the past few decades. At the same time, aircraft designers have had to respond to the need to ensure that the flight crew are not overburdened with information and that relevant data is presented in an appropriate form and at the time it is needed.

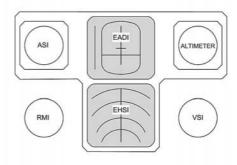

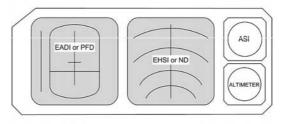

Figure 1.23 shows how the modern EFIS layouts have evolved progressively from the basic 'T' instrument configuration found in non-EFIS aircraft. Maintaining the relative position of the instruments has been important in allowing pilots to adapt from one aircraft type to another. At the same time, the large size of modern CRT and LCD displays, coupled with the ability of these instruments to display combined data (for example, heading, airspeed and altitude) has led to a less-cluttered instrument panel (see Figures 1.24 and 1.26). Lastly, a number of standby (or secondary) instruments are made available in order to provide the flight crew with reference information which may become invaluable in the case of a malfunction in the computer system.

(a) Basic 'T' flight instrument configuration

(b) Basic EFIS flight instrument configuration

(c) Enhanced EFIS flight instrument configuration

1.23 Evolution of instrument layouts

**1.24** Captain's flight instrument and display layout on the A320

#### **TEST YOUR UNDERSTANDING 1.5**

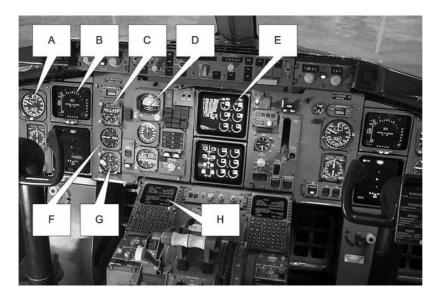

- 1. Identify each of the Boeing 767 flight instruments and displays shown in Figure 1.25.

- 2. Classify the flight instruments in Question 1 as either primary or standby.

**1.25** See Test your understanding 1.5

1.26 Upgraded flight instruments on an Aero Commander 690A

#### 1.3 MULTIPLE-CHOICE QUESTIONS

- 1. A multifunction display (MFD) can be:

- (a) used only for basic flight information

- (b) configured for more than one type of infor-

- (c) set to display information from the standby magnetic compass.

- 2. Which standby instruments are driven from the aircraft's pitot-static system:

- (a) Airspeed indicator, altimeter and vertical speed indicator

- (b) Airspeed indicator, vertical speed indicator and magnetic compass

- (c) Airspeed indicator, altimeter and angle-ofattack indicator.

- 3. Static pressure is fed:

- (a) only to the airspeed indicator

- (b) only to the airspeed indicator and vertical speed indicator

- (c) to the airspeed indicator as well as the altimeter and vertical speed indicator.

- 4. The horizontal situation indicator (HSI) uses information derived from:

- (a) the VOR receiver

- (b) the pitot-static system

- (c) the airspeed indicator.

- 5. The term 'glass cockpit' refers to:

- (a) the use of LCD and CRT displays

- (b) the use of toughened glass windows

- (c) the use of a transparent partition between the flight deck and passenger cabin.

- 6. Basic air data instruments are:

- (a) airspeed indicator, altimeter and magnetic

- (b) airspeed indicator, altimeter and vertical speed indicator

- airspeed indicator, vertical speed indicator and artificial horizon.

- 7. Three airborne parameters that can be used to assess aircraft position are:

- (a) airspeed, height and weight

- (b) heading, airspeed and height

- (c) heading, weight and airspeed.

- 8. The instrument shown in Figure 1.27 is the:

- (a) ADI

- (b) ASI

- (c) VSI.

- 9. Engine parameters such as turbine speed are displayed on:

- (a) ECAM

- (b) EHSI

- (c) EADI.

1.27 See Question 8

#### 14 AIRCRAFT DIGITAL ELECTRONIC AND COMPUTER SYSTEMS

- 10. The aircraft slip indicator is found in the:

- (a) EADI

- (b) ECAM

- (c) CRTs in the passenger cabin.

- 11. Where is the 'rising runway':

- (a) EADI

- (b) ECAM

- (c) CRTs in the passenger cabin.

- 12. Under visual flight rules (VFR) the pilot's most important source of information concerning the aircraft's position and attitude is:

- (a) the view out of the cockpit window

- (b) the altimeter and vertical speed indicators

- (c) the airspeed indicator and the magnetic compass.

- 13. The EFIS fitted to a large aircraft usually consists of:

- (a) a single multi-function display

- (b) separate primary flight and navigation displays

- (c) a primary display with several standby instruments.

- 14. The instrument shown in Figure 1.28 is the:

- (a) EADI

- (b) EHSI

- (c) ECAM.

- 15. The instrument shown in Figure 1.29 is the:

- (a) EADI

- (b) EHSI

- (c) ECAM.

- 16. In a basic 'T' configuration of instruments:

- (a) the ADI appears on the left and the ASI appears on the right

- (b) the ADI appears on the left and the HSI appears on the right

- (c) the ASI appears on the left and the altimeter appears on the right.

1.28 See Question 14

- **1.29** See Question 15

- 17. The flight director system receives information:

- (a) only from the VOR/localiser

- (b) only from the attitude gyro and altimeter

- (c) from both of the above.

- 18. EICAS provides the following information:

- (a) engine parameters only

- (b) engine parameters and system warnings

- (c) engine parameters and navigational data.

- 19. The two sets of flight regulations that a pilot may fly by are:

- (a) VFR and IFR

- (b) VHF and IFR

- (c) VFR and IFU.

- 20. Secondary heading information is obtained from:

- (a) the gyro

- (b) the compass

- (c) the pitot-static system.

- 21. A major advantage of EFIS is a reduction in:

- (a) effects of EMI

- (b) wiring and cabling

- (c) moving parts present in the flight deck.

- 22. The term 'artificial horizon' is sometimes used to describe the indication produced by:

- (a) the altimeter

- (b) the attitude indicator

- (c) the vertical speed indicator.

- 23. Typical displays on an EHSI are:

- (a) engine indications

- (b) VOR, heading, track

- (c) VOR, altitude, rate of climb.

- 24. In a basic 'T' configuration of instruments:

- (a) the ADI appears at the top and the HSI appears at the bottom

- (b) the HSI appears at the top and the ASI appears at the bottom

- (c) the ASI appears at the top and the ADI appears at the bottom.

- 25. Operational faults in FMS can be detected by:

- (a) automatically comparing outputs on a continuous basis

- (b) routine maintenance inspection of the aircraft

- (c) pre-flight checks.

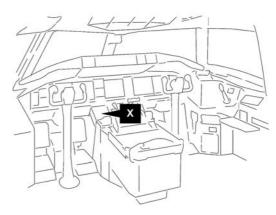

- 26. The display marked X in Figure 1.30 is the:

- (a) navigation display

- (b) primary flight display

- (c) FMS CDU.

**1.30** See Question 26

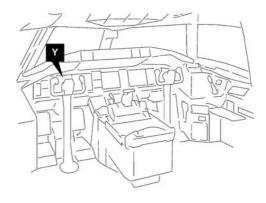

- **1.31** See Question 27

- 27. The display marked Y in Figure 1.31 is the:

- (a) standby flight instruments

- (b) primary flight display

- (c) FMS CDU.

- 28. The upper ECAM display provides:

- (a) navigation information

- (b) secondary flight information

- (c) engine parameters.

# 2 Number systems

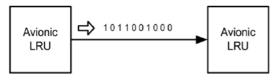

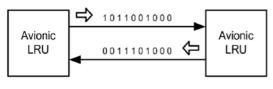

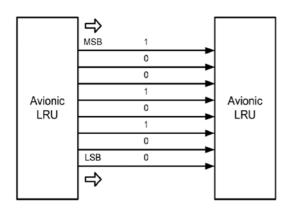

The signals in digital logic and computer systems are conveyed along individual electrical conductors and also using multiple wiring arrangements where several conductors are used to convey signals from one place to another in what is known as a bus system. As we will see in Chapter 4, the number of individual bus lines depends on the particular bus standard employed; however, signals on the individual lines, no matter what they are used for or how they are organised, can exist in only two basic states: logic 0 ('low' or 'off') or logic 1 ('high' or 'on'). Thus information within a digital system is represented in the form of a sequence of 1s and 0s, known as binary data.

Since binary numbers (particularly large ones) are not very convenient for human use, we often convert binary numbers to other forms of number that are easier to recognise and manipulate. These number systems include hexadecimal (base 16) and octal (base 8). This chapter is designed to introduce you to the different types of number system as well as the process of conversion from one type to another.

#### **TEST YOUR UNDERSTANDING 2.1**

Write down the values of:

- (a)  $2 \times 102$

- (b)  $3 \times 104$

- (c)  $(1 \times 103) + (9 \times 102) + (0 \times 101) + (1 \times 100)$ .

#### 2.1 DECIMAL (DENARY) NUMBERS

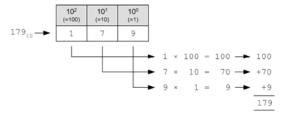

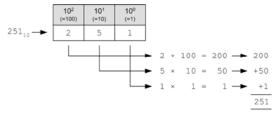

The decimal numbers that we are all very familiar with use the base 10 system. In this system the weight of each digit is ten times as great as the digit immediately to its right. The rightmost digit of a decimal integer (i.e. a whole number) is the unit's place (100); the digit to its left is the ten's digit (10<sup>1</sup>); the next is the hundred's digit (10<sup>2</sup>); and so on. The valid digits in a decimal number are 0 to 9. Figures 2.1 and 2.2

**2.1** An example showing how the decimal number 179 is constructed

**2.2** An example showing how the decimal number 251 is constructed

show two examples of how decimal numbers are constructed. Note that we have used the suffix '10' to indicate that the number is a decimal. So, 179<sub>10</sub> and 251<sub>10</sub> are both decimal (or base 10) numbers. The use of subscripts helps us to avoid confusion about what number base we are actually dealing with.

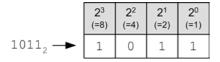

#### 2.2 BINARY NUMBERS

In the binary system (base 2), the weight of each digit is two times as great as the digit immediately to its right. The rightmost digit of a binary integer is the one's digit; the next digit to the left is the two's digit; next is the four's digit; then the eight's digit; and so on. The valid digits in the binary system are 0 and 1. Figure 2.3 shows an example of a binary number (note the use of the suffix '2' to indicate the number base).

The binary numbers that are equivalent to the decimal numbers 0 to 9 are shown in Table 2.1. Notice how the most significant digit (MSD) is shown on the

#### 2.3 Example of a binary number

**Table 2.1** Binary and decimal numbers

| Binary | Decimal |

|--------|---------|

| 0000   | 0       |

| 0001   | 1       |

| 0010   | 2       |

| 0011   | 3       |

| 0100   | 4       |

| 0101   | 5       |

| 0110   | 6       |

| 0111   | 7       |

| 1000   | 8       |

| 1001   | 9       |

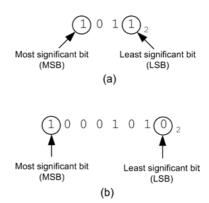

left and the least significant digit (LSD) appears on the right. In the table, the MSD has a weight of 2<sup>3</sup> (or 8 in decimal) while the LSD has a weight of 20 (or 1 in decimal). Since the MSD and LSD are represented by binary digits (either 0 or 1) we often refer to them as the most significant bit (MSB) and least significant bit (LSB), respectively, as shown in Figure 2.4.

2.4 MSB and LSB in binary numbers

#### **TEST YOUR UNDERSTANDING 2.2**

- 1. What is the binary value of (a) the MSB and (b) the LSB in the binary number 101100?

- 2. What is the binary weight of the MSB in the number 10001101?

#### 2.2.1 Binary to decimal conversion

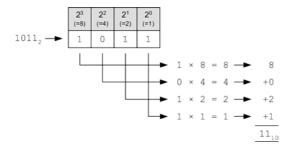

In order to convert a binary number to its equivalent decimal number we can determine the value of each successive binary digit, multiply it by the column value (in terms of the power of the base) and then simply add the values up. For example, to convert the binary number 1011, we take each digit and multiply it by the binary weight of the digit position (8, 4, 2 and 1) and add the result, as shown in Figure 2.5.

2.5 Example of binary to decimal conversion

#### 2.2.2 Decimal to binary conversion

There are two basic methods for converting decimal numbers to their equivalent in binary. The first method involves breaking the number down into a succession of numbers that are each powers of 2 and then placing the relevant digit (either a 0 or a 1) in the respective digit position, as shown in Figure 2.6.

$$23_{10} = 16 + 4 + 2 + 1$$

$$= (1 \times 2^{4}) + (0 \times 2^{3}) + (1 \times 2^{2}) + (1 \times 2^{1}) + (1 \times 2^{0})$$

$$2^{4} \quad 2^{3} \quad 2^{2} \quad 2^{1} \quad 2^{0}$$

$$(=16) \quad (=8) \quad (=4) \quad (=2) \quad (=1)$$

$$1 \quad 0 \quad 1 \quad 1 \quad 1$$

2.6 Example of decimal to binary conversion

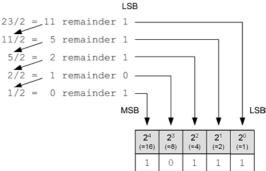

Another method involves successive division by two, retaining the remainder as a binary digit and then using the result as the next number to be divided, as shown in Figure 2.7. Note how the binary number is built up in reverse order, i.e. with the last remainder as the MSB and the first remainder as the LSB.

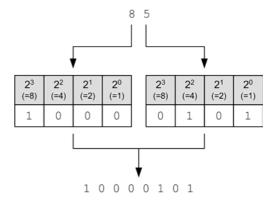

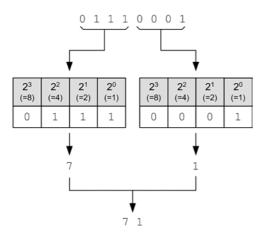

#### 2.2.3 Binary coded decimal

The system of binary numbers that we have looked at so far is more correctly known as natural binary. Another form of binary number commonly used in digital logic circuits is known as binary coded decimal (BCD). In this simpler system, binary conversion to

**2.7** Example of decimal to binary conversion using successive division

#### **TEST YOUR UNDERSTANDING 2.3**

- Convert the following binary numbers to decimal: (a) 10101; (b) 110011; (c) 1001001; (d) 10101011.

- 2. Convert the following decimal numbers to binary: (a) 25; (b) 43; (c) 65; (d) 100.

and from decimal numbers involves arranging binary numbers in groups of four binary digits from right to left, each of which corresponds to a single decimal digit, as shown in Figures 2.8 and 2.9.

**2.8** Example of converting the decimal number 85 to binary coded decimal (BCD)

**2.9** Example of converting the BCD number 01110001 to decimal

#### **TEST YOUR UNDERSTANDING 2.4**

- 1. Convert the following decimal numbers to BCD: (a) 97; (b) 6450.

- 2. Convert the following BCD numbers to decimal: (a) 10000011: (b) 011111101001.

#### 2.2.4 One's complement

The one's complement of a binary number is formed by inverting the value of each digit of the original binary number (i.e. replacing 1s with 0s and 0s with 1s). So, for example, the one's complement of the binary number 1010 is simply 0101. Similarly, the one's complement of 01110001 is 10001110. Note that if you add the one's complement of a number to the original number the result will be all 1s, as shown in Figure 2.10.

**2.10** The result of adding the one's complement of a number to the original number

#### 2.2.5 Two's complement

Two's complement notation is frequently used to represent negative numbers in computer mathematics (with only one possible code for zero – unlike one's complement notation). The two's complement of a binary number is formed by inverting the digits of the original binary number and then adding 1 to the result. So, for example, the two's complement of the binary number 1001 is 0111. Similarly, the two's complement of 01110001 is 10001111. When two's complement notation is used to represent negative numbers the MSD is always a 1. Figure 2.11 shows two examples of finding the two's complement of a binary number. In the case of Figure 2.11b it is important to note the use of a carry digit when performing the binary addition.

**2.11** Method of finding the two's complement of a binary number

#### 2.3 OCTAL NUMBERS

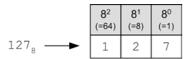

The octal number system is used as a more compact way of representing binary numbers. Because octal consists of eight digits (0 to 7), a single octal digit can replace three binary digits. Put another way, by arranging a binary number into groups of three binary digits (or bits) we can replace each group by a single octal digit (see Figure 2.12). Note that, in a similar manner to the numbering systems that we met previously in this chapter, the weight of each digit in an octal number is eight times as great as the digit immediately to its right. The rightmost digit of an octal number is the unit's place  $(8^0)$ , the digit to its left is the eight's digit  $(8^1)$ , the next is the 64's digit  $(8^2)$ , and so on.

2.12 Example of an octal number

#### **TEST YOUR UNDERSTANDING 2.5**

- Find the one's complement of the binary number 100010.

- 2. Find the two's complement of the binαry number 101101.

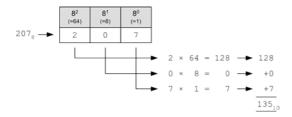

#### 2.3.1 Octal to decimal conversion

In order to convert a binary number to a decimal number we can determine the value of each successive octal digit, multiply it by the column value (in terms of the power of the base) and simply add the values up. For example, the octal number 207 is converted by taking each digit and then multiplying it by the octal weight of the digit position and adding the result, as shown in Figure 2.13.

2.13 Example of octal to decimal conversion

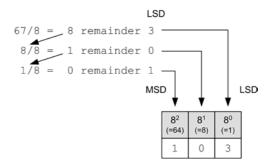

#### 2.3.2 Decimal to octal conversion

As with decimal to binary conversion, there are two methods for converting decimal numbers to octal. The first method involves breaking the number down into a succession of numbers that are each powers of 8 and then placing the relevant digit (having a value between 0 and 7) in the respective digit position, as shown in Figure 2.14.

2.14 Example of decimal to octal conversion

The other method of decimal to octal conversion involves successive division by eight, retaining the remainder as a digit (with a value between 0 and 7) before using the result as the next number to be divided, as shown in Figure 2.15. Note how the octal number is built up in reverse order, i.e. with the last remainder as the MSD and the first remainder as the LSD.

**2.15** Example of decimal to octal conversion using successive division

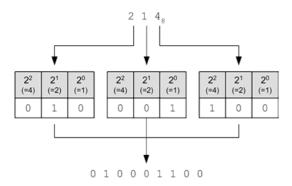

#### 2.3.3 Octal to binary conversion

In order to convert an octal number to a binary number we simply convert each digit of the octal number to its corresponding three-bit binary value, as shown in Figure 2.16.

2.16 Example of octal to binary conversion

#### 2.3.4 Binary to octal conversion

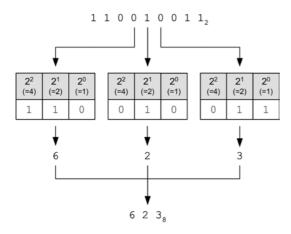

Converting a binary number to its equivalent in octal is also extremely easy. In this case you simply need to arrange the binary number in groups of three binary digits from right to left and then convert each group to its equivalent octal number, as shown in Figure 2.17.

2.17 Example of binary to octal conversion

#### 2.4 HEXADECIMAL NUMBERS

Although computers are quite comfortable working with binary numbers of 8, 16 or even 32 binary digits, humans find it inconvenient to work with so many digits at a time. The hexadecimal (base 16) numbering system offers a practical compromise acceptable to both humans and machines. One hexadecimal digit can represent four binary digits, thus an 8-bit binary number can be expressed using two hexadecimal digits. For example, 10000011 binary is the same as 83 when expressed in hexadecimal.

The correspondence between a hexadecimal (hex) digit and the four binary digits it represents is quite straightforward and easy to learn (see Table 2.2). Note that in hexadecimal the decimal numbers from 10 to 15 are represented by the letters A to F, respectively. Furthermore, conversion between binary

**Table 2.2** Binary, decimal, hexadecimal and octal numbers

| Binary | Decimal | Hexadecimal | Octal |

|--------|---------|-------------|-------|

| 0000   | 0       | 0           | 0     |

| 0001   | 1       | 1           | 1     |

| 0010   | 2       | 2           | 2     |

| 0011   | 3       | 3           | 3     |

| 0100   | 4       | 4           | 4     |

| 0101   | 5       | 5           | 5     |

| 0110   | 6       | 6           | 6     |

| 0111   | 7       | 7           | 7     |

| 1000   | 8       | 8           | 10    |

| 1001   | 9       | 9           | 11    |

| 1010   | 10      | A           | 12    |

| 1011   | 11      | В           | 13    |

| 1100   | 12      | С           | 14    |

| 1101   | 13      | D           | 15    |

| 1110   | 14      | E           | 16    |

| 1111   | 15      | F           | 17    |

and hexadecimal is fairly straightforward by simply arranging the binary digits in groups of four bits (starting from the least significant). Hexadecimal notation is much more compact than binary notation and easier to work with than decimal notation.

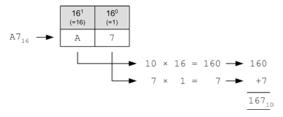

#### 2.4.1 Hexadecimal to decimal conversion

In order to convert a hexadecimal number to a decimal number we can determine the value of each successive hexadecimal digit, multiply it by the column value (in terms of the power of the base) and simply add the values up. For example, the hexadecimal number of A7 is converted by taking each digit and then multiplying it by the weight of the digit position, as shown in Figure 2.18.

2.18 Example of hexadecimal to decimal conversion

# 2.4.2 Decimal to hexadecimal to conversion

In order to convert a decimal number to its hexadecimal equivalent you can break the number down into a succession of numbers that are each powers of 16, and then place the relevant digit (a value between 0 and F) in the respective digit position, as shown in Figure 2.19. Note how, in the case of the example shown in Figure 2.19b the letters F and E, respectively, replace the decimal numbers 15 and 14.

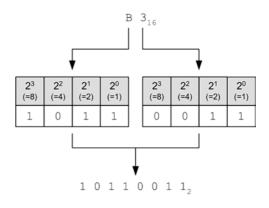

#### 2.4.3 Hexadecimal to binary conversion

In order to convert a hexadecimal number to a binary number we simply need to convert each digit of the hexadecimal number to its corresponding four-bit binary value, as shown in Figure 2.20. The method is similar to that which you used earlier to convert octal numbers to their binary equivalents.

$$103_{10} = 96 + 7$$

$$= (6 \times 16^{1}) + (7 \times 16^{0})$$

$$\begin{array}{r} 16^{1} & 16^{0} \\ (=16) & (=1) \\ \hline 6 & 7 \end{array}$$

(a)

$$254_{10} = 240 + 14$$

$$= (15 \times 16^{1}) + (14 \times 16^{0})$$

$$\begin{array}{r} 16^{1} & 16^{0} \\ (=16) & (=1) \\ \hline F & E \end{array}$$

(b)

**2.19** Example of decimal to hexadecimal conversion

**2.20** Example of hexadecimal to binary conversion

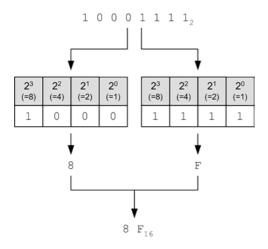

# 2.4.4 Binary to hexadecimal conversion

Converting a binary number to its equivalent in hexadecimal is also extremely easy. In this case you simply need to arrange the binary number in groups of four binary digits, working from right to left, before converting each group to its hexadecimal equivalent, as shown in Figure 2.21. Once again, the

2.21 Example of binary to hexadecimal conversion

method is similar to that which you used earlier to convert binary numbers to their octal equivalents.

#### **TEST YOUR UNDERSTANDING 2.6**

- 1. Find the decimal equivalent of the octal number 41.

- 2. Find the octal equivalent of the decimal number 139.

- 3. Find the binary equivalent of the octal number 537.

- 4. Find the octal equivalent of the binary number 111001100.

- 5. Convert the hexadecimal number 3F to: (a) decimal; (b) binary.

- 6. Convert the binary number 101111001 to: (a) octal: (b) hexadecimal.

- 7. Which of the following numbers is the largest? (a) C5<sub>16</sub>; (b) 11000001<sub>2</sub>; (c) 303<sub>8</sub>.

# 2.5 AMERICAN STANDARD CODE FOR INFORMATION INTERCHANGE

While not a system of numbers, the American Standard Code for Information Interchange (ASCII) is important as it provides us with a way of representing printable characters using binary, decimal or hexadecimal numbers. ASCII is the means by which computers are able to store and exchange alphanumeric data with other computers and peripheral devices such as character-based displays and printers.

Standard ASCII is based on a 7-bit binary code and caters for a total of 128 (2<sup>7</sup>) alphanumeric characters (both upper and lower case), punctuation and special control characters. Extended ASCII employs an eighth (leading) bit to provide an additional 128 characters from a single 8-bit byte.

The first 32 ASCII characters (corresponding to hexadecimal codes 00 to 1F) are non-printing control characters used to facilitate data transfer and control peripherals such as character-based displays and printers.

The ASCII printable characters (corresponding to hexadecimal codes 20 to 7F) represent letters, numbers, punctuation and a few miscellaneous symbols (see Table 2.3). Note that the first of these characters (32 decimal) corresponds to the space character that doesn't actually print!

#### **TEST YOUR UNDERSTANDING 2.7**

- 1. Convert the ASCII data 00110000 00111001 01011100 to printable alphanu-

- 2. Convert the alphanumeric text 'TCAS' to ASCII data.

#### **KEY POINT**

ASCII uses seven binary digits to represent control codes. The basic 7-bit ASCII character additional leading digit to form an 8-bit code; each character of the extended ASCII character set is then represented by a single byte (8-bits) of data.

**Table 2.3** Decimal, octal, hexadecimal, binary and ASCII values

| Decimal | Octal | Hexadecimal | Binary   | ASCII | Meaning                  |

|---------|-------|-------------|----------|-------|--------------------------|

| 0       | 000   | 00          | 00000000 | NUL   | Null                     |

| 1       | 001   | 01          | 00000001 | SOH   | Start of heading         |

| 2       | 002   | 02          | 00000010 | STX   | Start of text            |

| 3       | 003   | 03          | 00000011 | ETX   | End of text              |

| 4       | 004   | 04          | 00000100 | EOT   | End of transmission      |

| 5       | 005   | 05          | 00000101 | ENQ   | Enquiry                  |

| 6       | 006   | 06          | 00000110 | ACK   | Acknowledgement          |

| 7       | 007   | 07          | 00000111 | BEL   | Bell                     |

| 8       | 010   | 08          | 00001000 | BS    | Backspace                |

| 9       | 011   | 09          | 00001001 | HT    | Horizontal tab           |

| 10      | 012   | 0A          | 00001010 | LF    | Line feed                |

| 11      | 013   | ОВ          | 00001011 | VT    | Vertical tab             |

| 12      | 014   | 0C          | 00001100 | FF    | Form feed                |

| 13      | 015   | 0D          | 00001101 | CR    | Carriage return          |

| 14      | 016   | 0E          | 00001110 | SO    | Shift out                |

| 15      | 017   | 0F          | 00001111 | SI    | Shift in                 |

| 16      | 020   | 10          | 00010000 | DLE   | Data line escape         |

| 17      | 021   | 11          | 00010001 | DC1   | Device control 1         |

| 18      | 022   | 12          | 00010010 | DC2   | Device control 2         |

| 19      | 023   | 13          | 00010011 | DC3   | Device control 3         |

| 20      | 024   | 14          | 00010100 | DC4   | Device control 4         |

| 21      | 025   | 15          | 00010101 | NAK   | Negative acknowledgement |

| 22      | 026   | 16          | 00010110 | SYN   | Synchronous idle         |

| 23      | 027   | 17          | 00010111 | ETB   | End of transmit block    |

| 24      | 030   | 18          | 00011000 | CAN   | Cancel                   |

| 25      | 031   | 19          | 00011001 | EM    | End of medium            |

| 26      | 032   | 1A          | 00011010 | SUB   | Substitute               |

| 27      | 033   | 1B          | 00011011 | ESC   | Escape                   |

| Decimal | Octal | Hexadecimal | Binary   | ASCII | Meaning           |

|---------|-------|-------------|----------|-------|-------------------|

| 28      | 034   | 1C          | 00011100 | FS    | File separator    |

| 29      | 035   | 1D          | 00011101 | GS    | Group separator   |

| 30      | 036   | 1E          | 00011110 | RS    | Record separator  |

| 31      | 037   | 1F          | 00011111 | US    | Unit separator    |

| 32      | 040   | 20          | 00100000 |       | Space             |

| 33      | 041   | 21          | 00100001 | !     | Exclamation mark  |

| 34      | 042   | 22          | 00100010 | "     | Double quotes     |

| 35      | 043   | 23          | 00100011 | #     | Number            |

| 36      | 044   | 24          | 00100100 | \$    | Dollar            |

| 37      | 045   | 25          | 00100101 | %     | Percent           |

| 38      | 046   | 26          | 00100110 | &     | Ampersand         |

| 39      | 047   | 27          | 00100111 | 6     | Single quote      |

| 40      | 050   | 28          | 00101000 | (     | Open parenthesis  |

| 41      | 051   | 29          | 00101001 | )     | Close parenthesis |

| 42      | 052   | 2A          | 00101010 | *     | Asterisk          |

| 43      | 053   | 2B          | 00101011 | +     | Plus              |

| 44      | 054   | 2C          | 00101100 | ,     | Comma             |

| 45      | 055   | 2D          | 00101101 | -     | Hyphen            |

| 46      | 056   | 2E          | 00101110 |       | Full stop         |

| 47      | 057   | 2F          | 00101111 | 1     | Divide            |

| 48      | 060   | 30          | 00110000 | 0     | Zero              |

| 49      | 061   | 31          | 00110001 | 1     | One               |

| 50      | 062   | 32          | 00110010 | 2     | Two               |

| 51      | 063   | 33          | 00110011 | 3     | Three             |

| 52      | 064   | 34          | 00110100 | 4     | Four              |

| 53      | 065   | 35          | 00110101 | 5     | Five              |

| 54      | 066   | 36          | 00110110 | 6     | Six               |

| 55      | 067   | 37          | 00110111 | 7     | Seven             |

| 56      | 070   | 38          | 00111000 | 8     | Eight             |

Table 2.3 continued

| Decimal | Octal | Hexadecimal | Binary   | ASCII | Meaning       |

|---------|-------|-------------|----------|-------|---------------|

| 57      | 071   | 39          | 00111001 | 9     | Nine          |

| 58      | 072   | 3A          | 00111010 | :     | Colon         |

| 59      | 073   | 3B          | 00111011 | ;     | Semicolon     |

| 60      | 074   | 3C          | 00111100 | <     | Less than     |

| 61      | 075   | 3D          | 00111101 | =     | Equals        |

| 62      | 076   | 3E          | 00111110 | >     | Greater than  |

| 63      | 077   | 3F          | 00111111 | ?     | Question mark |

| 64      | 100   | 40          | 01000000 | @     | At symbol     |

| 65      | 101   | 41          | 01000001 | А     | Uppercase A   |

| 66      | 102   | 42          | 01000010 | В     | Uppercase B   |

| 67      | 103   | 43          | 01000011 | С     | Uppercase C   |

| 68      | 104   | 44          | 01000100 | D     | Uppercase D   |

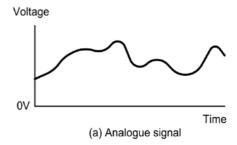

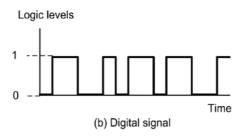

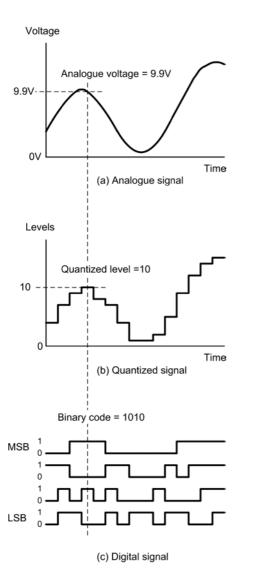

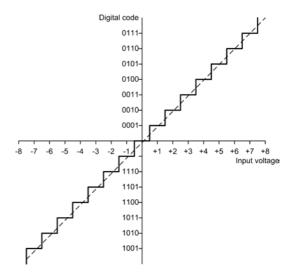

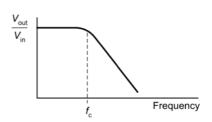

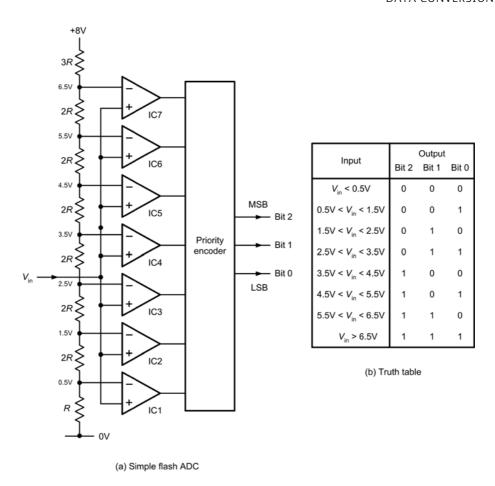

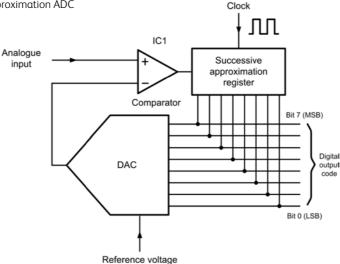

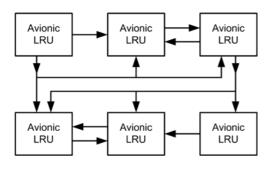

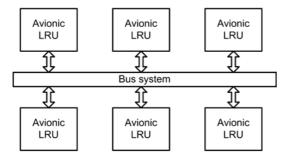

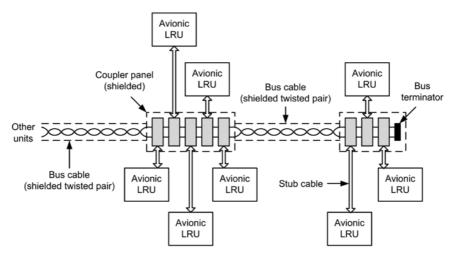

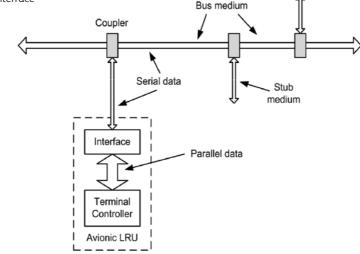

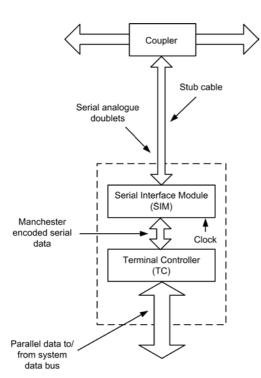

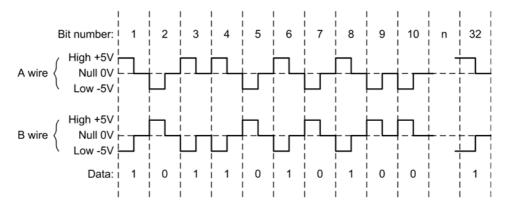

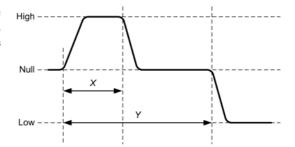

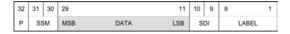

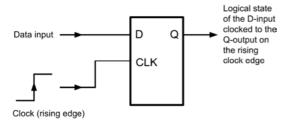

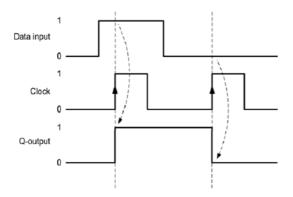

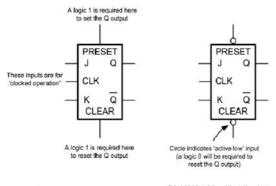

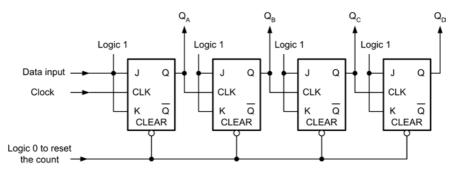

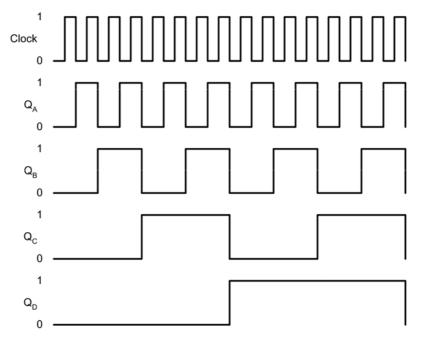

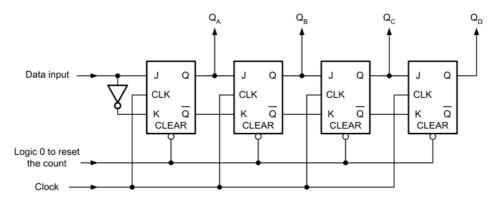

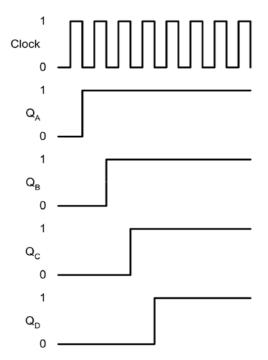

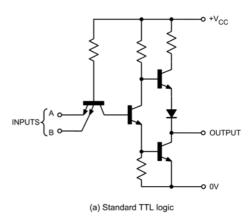

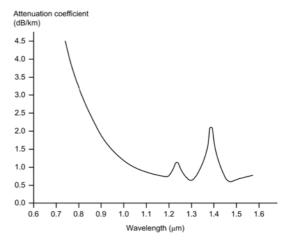

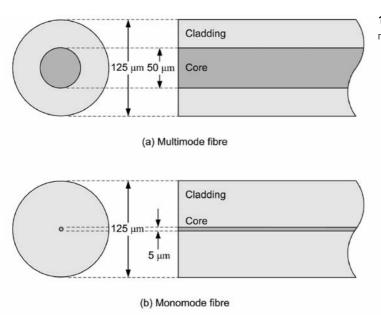

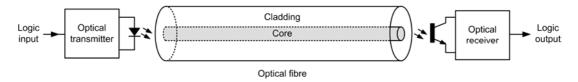

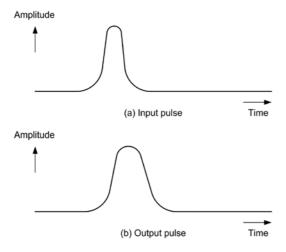

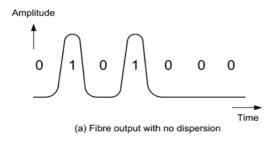

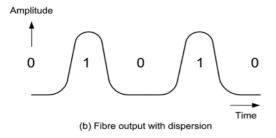

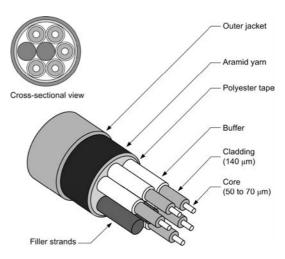

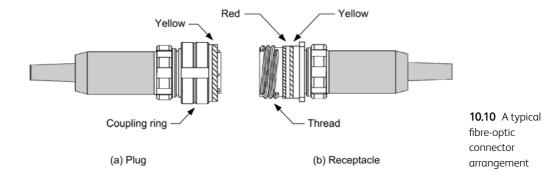

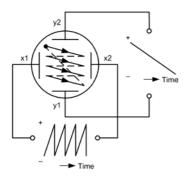

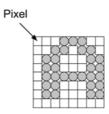

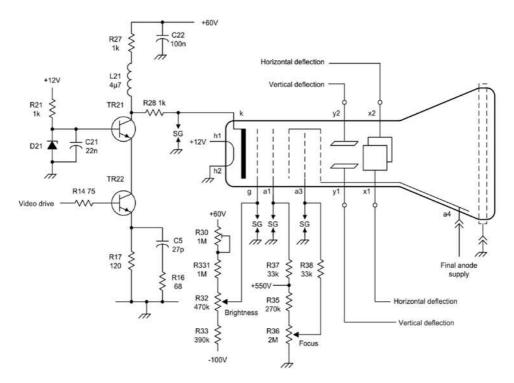

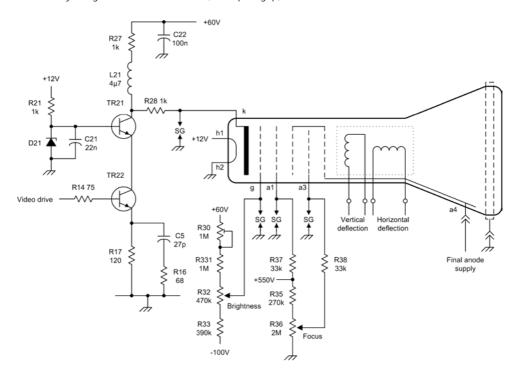

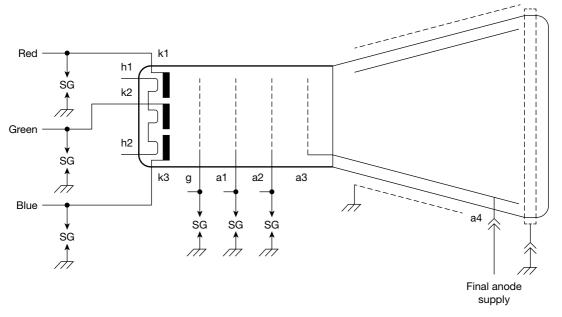

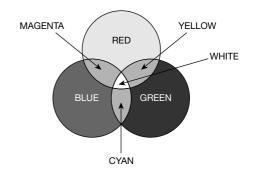

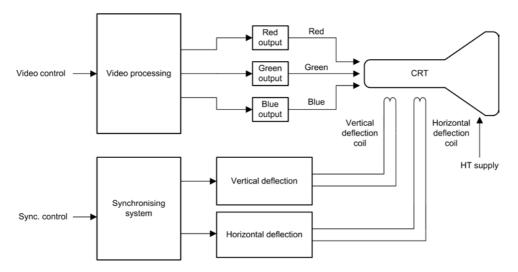

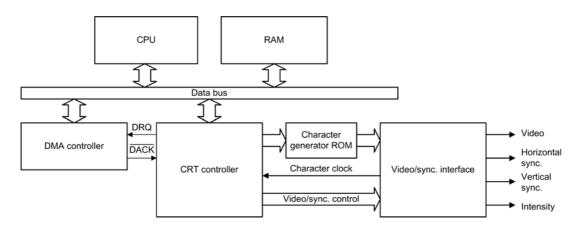

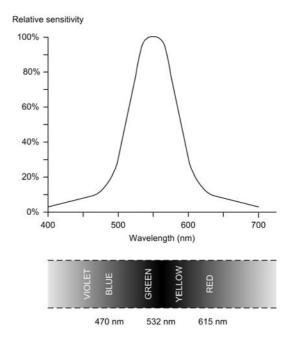

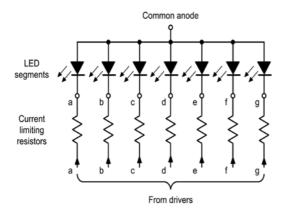

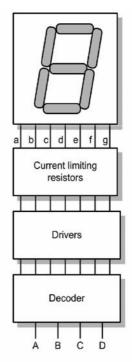

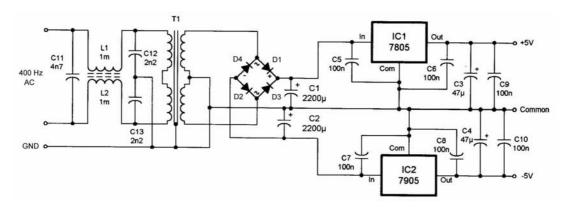

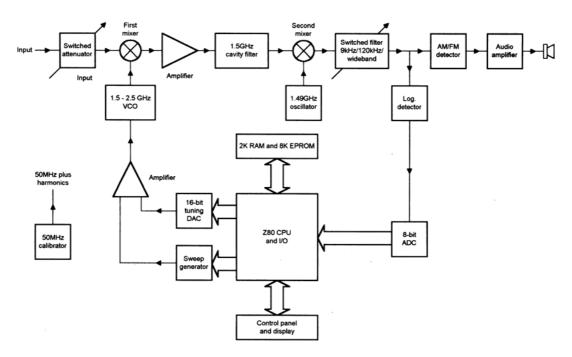

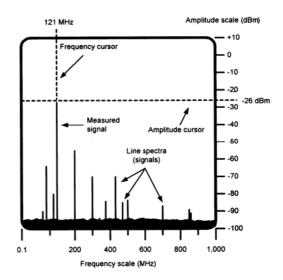

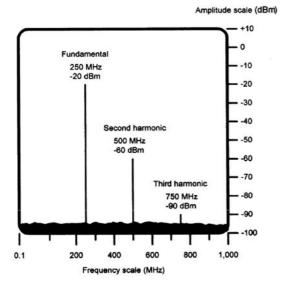

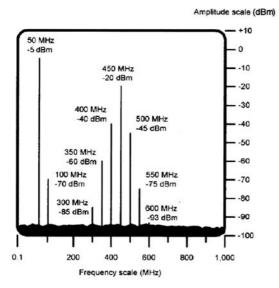

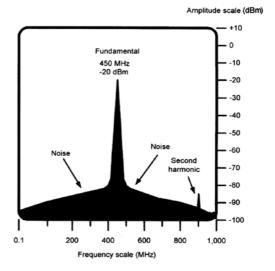

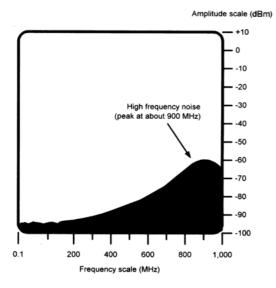

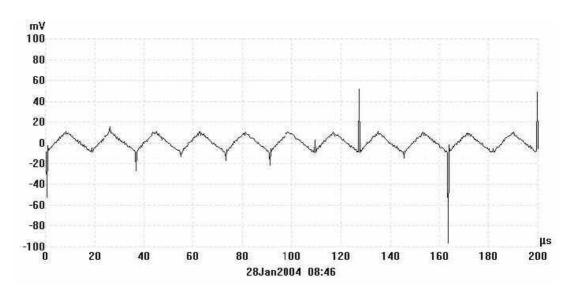

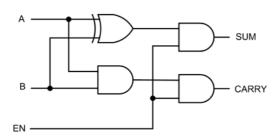

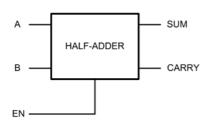

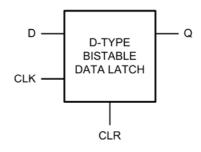

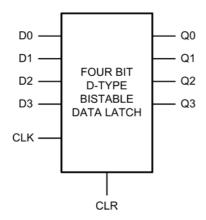

| 69      | 105   | 45          | 01000101 | Е     | Uppercase E   |